# SBC

## User Manual

# SBC-C43

Single Board Computer with NXP i.MX 8 Applications Processors in 3.5" form factor

## **REVISION HISTORY**

| Revision | Date                           | Note                    | Ref |

|----------|--------------------------------|-------------------------|-----|

| 1.0      | 17 <sup>th</sup> November 2020 | First Official Release. | AR  |

|          |                                |                         |     |

All rights reserved. All information contained in this manual is proprietary and confidential material of SECO S.p.A.

Unauthorized use, duplication, modification or disclosure of the information to a third-party by any means without prior consent of SECO S.p.A. is prohibited.

Every effort has been made to ensure the accuracy of this manual. However, SECO S.p.A. accepts no responsibility for any inaccuracies, errors or omissions herein. SECO S.p.A. reserves the right to change precise specifications without prior notice to supply the best product possible.

For further information on this module or other SECO products, but also to get the required assistance for any and possible issues, please contact us using the dedicated web form available at http://www.seco.com (registration required).

Our team is ready to assist.

## INDEX

| 5        |

|----------|

| 6        |

| 7        |

| 7        |

| 8        |

| 8        |

| 8        |

| 9        |

| 11       |

| 12       |

| 13       |

| 14       |

| 15       |

| 15       |

| 16       |

| 16       |

| 17<br>18 |

| 18<br>19 |

| 20       |

| 21       |

| 21       |

| 22       |

| 23       |

| 23       |

| 25       |

| 27       |

| 28       |

| 29       |

| 30       |

|          |

| 3.3.7      | USB Connectors                            | 32   |

|------------|-------------------------------------------|------|

| 3.3.8      | M.2 2230 Socket 1 Key E Connectivity Slot | 33   |

| 3.3.9      | M.2 SSD/WWAN Slot: Socket 2 Key B.        | 34   |

| 3.3.10     | microSIM Card Slot                        | 36   |

| 3.3.11     | microSD Slot                              | 36   |

| 3.3.12     | CAN Connectors                            | 37   |

| 3.3.13     | Expansion connectors                      | 38   |

| 3.3.14     | A/D Header                                | 39   |

| 3.3.15     | Debug UART Connector                      | . 40 |

| 3.3.16     | JTAG Connector                            | . 40 |

| 3.3.17     | Power and Reset buttons                   | . 40 |

| 3.3.18     | Boot Mode Selection jumper JP2            | . 40 |

| Chapter 4. | APPENDICES                                | . 41 |

| 4.1 The    | rmal Design                               | 42   |

# Chapter 1. INTRODUCTION

- Warranty

- Information and assistance

- RMA number request

- Safety

- Electrostatic discharges

- RoHS compliance

- Terminology and definitions

- Reference specifications

## 1.1 Warranty

This product is subject to the Italian Law Decree 24/2002, acting European Directive 1999/44/CE on matters of sale and warranties to consumers.

The warranty on this product lasts for 1 year.

Under the warranty period, the Supplier guarantees the buyer assistance and service for repairing, replacing or credit of the item, at the Supplier's own discretion.

Shipping costs that apply to non-conforming items or items that need replacement are to be paid by the customer.

Items cannot be returned unless previously authorized by the supplier.

The authorization is released after completing the specific form available on the web-site <a href="https://www.seco.com/it/support/online-rma.html">https://www.seco.com/it/support/online-rma.html</a> (RMA Online). The RMA authorization number must be put both on the packaging and on the documents shipped with the items, which must include all the accessories in their original packaging, with no signs of damage to, or tampering with, any returned item.

The error analysis form identifying the fault type must be completed by the customer and has must accompany the returned item.

If any of the above-mentioned requirements for RMA is not satisfied, the item will be shipped back and the customer will have to pay any and all shipping costs.

Following a technical analysis, the supplier will verify if all the requirements, for which a warranty service applies, are met. If the warranty cannot be applied, the Supplier will calculate the minimum cost of this initial analysis on the item and the repair costs. Costs for replaced components will be calculated separately.

Warning!

All changes or modifications to the equipment not explicitly approved by SECO S.p.A. could impair the equipment's functionalities and could void the warranty

## 1.2 Information and assistance

What do I have to do if the product is faulty?

SECO S.p.A. offers the following services:

- SECO website: visit <a href="http://www.seco.com">http://www.seco.com</a> to receive the latest information on the product. In most of the cases it is possible to find useful information to solve the problem.

- SECO Sales Representative: the Sales Rep can help to determine the exact cause of the problem and search for the best solution.

- SECO Help-Desk: contact SECO Technical Assistance. A technician is at disposal to understand the exact origin of the problem and suggest the correct solution.

E-mail: technical.service@seco.com

Fax (+39) 0575 350210

- Repair center: it is possible to send the faulty product to the SECO Repair Centre. In this case, follow this procedure:

- o Returned items must be accompanied by an RMA Number. Items sent without the RMA number will be not accepted.

- o Returned items must be shipped in an appropriate package. SECO is not responsible for damages caused by accidental drop, improper usage, or customer neglect.

Note: Please have the following information before asking for technical assistance:

- Name and serial number of the product;

- Description of Customer's peripheral connections;

- Description of Customer's software (operative system, version, application software, etc.);

- A complete description of the problem;

- The exact words of every kind of error message encountered.

## 1.3 RMA number request

To request an RMA number, please visit SECO's web-site. On the home page, please select "CONTACT US" then "Online RMA" and follow the procedure described. An RMA Number will be sent within 1 working day (only for on-line RMA requests).

## 1.4 Safety

The SBC-C43 board uses only extremely-low voltages.

While handling the board, please use extreme caution to avoid any kind of risk or damages to electronic components.

Always switch the power off, and unplug the power supply unit, before handling the board and/or connecting cables or other boards.

Avoid using metallic components - like paper clips, screws and similar - near the board when connected to a power supply, to avoid short circuits due to unwanted contacts with other board components.

If the board has become wet, never connect it to any external power supply unit or battery.

Check carefully that all cables are correctly connected and that they are not damaged.

## 1.5 Electrostatic discharges

The SBC-C43 board, like any other electronic product, is an electrostatic sensitive device: high voltages caused by static electricity could damage some or all the devices and/or components on-board.

Whenever handling an SBC-C43 board, ground yourself through an anti-static wrist strap. Placement of the board on an anti-static surface is also highly recommended.

## 1.6 RoHS compliance

The SBC-C43 board is designed using RoHS compliant components and is manufactured on a lead-free production line. It is therefore fully RoHS compliant.

## 1.7 Terminology and definitions

API Application Program Interface, a set of commands and functions that can be used by programmers for writing software for specific Operating

Systems

CAN Bus Controller Area network, a protocol designed for in-vehicle communication

CEC Consumer Electronics Control, an HDMI feature which allows controlling more devices connected together by using only one remote control

CSI2 MIPI Camera Serial Interface, 2nd generation standard regulating communication between a peripheral device (camera) and a host processor

DDC Display Data Channel, a kind of I2C interface for digital communication between displays and graphics processing units (GPU)

DDR Double Data Rate, a typology of memory devices which transfer data both on the rising and on the falling edge of the clock

eDP embedded Display Port

GbE Gigabit Ethernet

Gbps Gigabits per second

GND Ground

GPI/O General purpose Input/Output

GPU Graphics Processing Unit

HDMI High Definition Multimedia Interface, a digital audio and video interface

Inter-Integrated Circuit Bus, a simple serial bus consisting only of data and clock line, with multi-master capability

Inter-Integrated Circuit Sound, an audio serial bus protocol interface developed by Philips (now NXP) in 1986

LVDS Low Voltage Differential Signaling, a standard for transferring data at very high speed using inexpensive twisted pairs copper cables, usually used

for video applications

LPDDR4 Low-Power Double Data Rate Synchronous Dynamic Random Access Memory, 4<sup>th</sup> generation

MAC Medium Access Controller, the hardware implementing the Data Link Layer of ISO/OSI-7 model for communication systems

Mbps Megabits per second

MMC/eMMC MultiMedia Card / embedded MMC, a type of memory card, having the same interface of SD. The eMMC are the embedded version of the MMC.

They are devices that incorporate both the memory controller and the flash memories on a single BGA chip

N.A. Not ApplicableN.C. Not Connected

OpenGL Open Graphics Library, an Open Source API dedicated to 2D and 3D graphics

Open Vector Graphics, an Open Source API dedicated to hardware accelerated 2D vector graphics

OS Operating System

OTG On-the-Go, a specification that allows to USB devices to act indifferently as Host or as a Client, depending on the device connected to the port

PCI-e Peripheral Component Interface Express

PHY Abbreviation of Physical, it is the device implementing the Physical Layer of ISO/OSI-7 model for communication systems

PSU Power Supply Unit

PWM Pulse Width Modulation

PWR Power

RGMII Reduced Gigabit Media Independent Interface, a particular interface defining the communication between an Ethernet MAC and a PHY

SATA Serial Advance Technology Attachment, a differential half duplex serial interface for Hard Disks

SD Secure Digital, a memory card type

SM Bus System Management Bus, a subset of the I2C bus dedicated to communication with devices for system management, like a smart battery and

other power supply-related devices

SPI Serial Peripheral Interface, a 4-Wire synchronous full-duplex serial interface which contemplates a master and one or more slaves, individually

enabled through a Chip Select line

TBM To be measured

TMDS Transition-Minimized Differential Signalling, a method for transmitting high speed serial data, normally used on DVI and HDMI interfaces

TTL Transistor-transistor Logic

USB Universal Serial Bus

uSDHC Ultra Secure Digital Host Controller

V\_REF Voltage reference Pin

## 1.8 Reference specifications

Here below it is a list of applicable industry specifications and reference documents.

| Reference           | Link                                                                                                                                                                                                                |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACPI                | https://uefi.org/specifications                                                                                                                                                                                     |

| CAN Bus             | http://esd.cs.ucr.edu/webres/can20.pdf                                                                                                                                                                              |

| CSI                 | http://www.mipi.org/specifications/camera-interface                                                                                                                                                                 |

| DDC                 | http://www.vesa.org                                                                                                                                                                                                 |

| DP, eDP             | http://www.vesa.org                                                                                                                                                                                                 |

| FastEthernet        | http://standards.ieee.org/about/get/802/802.3.html                                                                                                                                                                  |

| Gigabit Ethernet    | http://standards.ieee.org/about/get/802/802.3.html                                                                                                                                                                  |

| HDMI                | http://www.hdmi.org/index.aspx                                                                                                                                                                                      |

| I2C                 | http://www.nxp.com/documents/other/UM10204_v5.pdf                                                                                                                                                                   |

| I2S                 | https://www.sparkfun.com/datasheets/BreakoutBoards/I2SBUS.pdf                                                                                                                                                       |

| LVDS                | http://www.ti.com/ww/en/analog/interface/lvds.shtml<br>http://www.ti.com/lit/ug/snla187/snla187.pdf                                                                                                                 |

| M.2 Specifications  | https://pcisig.com/specifications/pciexpress/M.2 Specification/                                                                                                                                                     |

| MMC/eMMC            | https://www.jedec.org/committees/jc-64                                                                                                                                                                              |

| NXP i.MX8 processor | https://www.nxp.com/products/processors-and-microcontrollers/arm-processors/i-mx-applications-processors/i-mx-8-processors/i-mx-8-family-arm-cortex-a53-cortex-a72-virtualization-vision-3d-graphics-4k-video:i.MX8 |

| OpenGL              | http://www.opengl.org                                                                                                                                                                                               |

| OpenVG              | http://www.khronos.org/openvg                                                                                                                                                                                       |

| PCI Express         | http://www.pcisig.com/specifications/pciexpress                                                                                                                                                                     |

| SD Card Association | https://www.sdcard.org                                                                                                                                                                                              |

| SM Bus              | http://www.smbus.org/specs                                                                                                                                                                                          |

| TMDS                | http://www.siliconimage.com/technologies/tmds                                                                                                                                                                       |

| USB 2.0 and USB OTG | https://www.usb.org/sites/default/files/usb_20_20190524.zip                                                                                                                                                         |

| USB 3.0             | http://www.usb.org/developers/docs/usb_30_spec_070113.zip                                                                                                                                                           |

# Chapter 2. OVERVIEW

- Introduction

- Technical specifications

- Electrical specifications

- Mechanical specifications

- Block diagram

## 2.1 Introduction

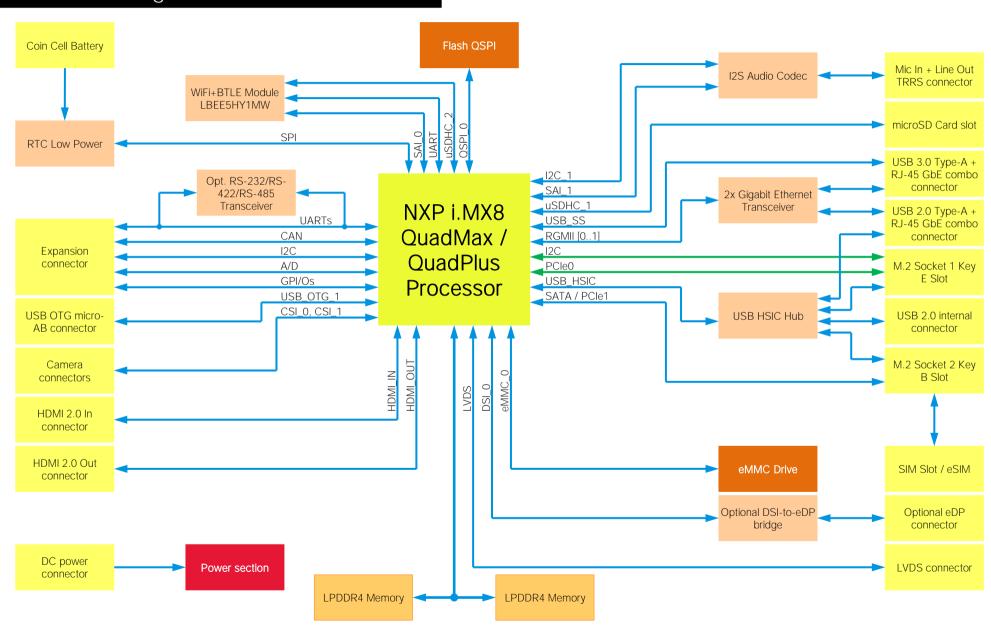

SBC-C43 is a Single Board Computer, measuring just 102 x 146 mm (4,02" x 5,75") based on embedded NXP i.MX 8 Family, featuring multicore processing (Single or Dual ARM Cortex®-A72 cores + Quad ARM Cortex®-A53 cores + Dual general purpose Cortex®-M4 processor).

Graphics features of the board are managed directly by NXP i.MX8 processor, which integrate 2x Graphics accelerators Vivante GC7000 / XVSX or GC7000 Lite / XVSX (QuadMax and QuadPlus) GPUs, supporting OpenGL® ES 1.1 / 2.0 / 3.0 / 3.1, Open CL 1.2 OpenGL 3.x, DirectX 11. This family of processors integrate one embedded VPU, which allows HW acceleration for video decoding of H.265 (4K30), H.264 (1080p60) and encoding of H.264 (1080p30).

The board is completed with up to 8GB LPDDR4 directly soldered on board, and one eMMC Flash Drive, directly accessible like any standard Drive, with up to 64GB of capacity. Mass storage capabilities are completed by a microSD Card slot. External SSD modules can expand mass storage capabilities through M.2 Key B Slot with S-ATA interface (factory option with PCle x1 for plugging M.2 Modem modules)

The processor offers two RGMII interfaces which, through dedicated Ethernet Transceivers, allows the implementation of two Gigabit Ethernet interfaces.

The communication / networking capabilities of the board are completed by an M.2 Key B Slot, which allows plugging M.2 Modem modules with USB or PCI-e interface, an M.2 Key E Slot, which allows plugging M.2 WiFi + BT modules with USB or PCI-e interface and by an optional WiFi a/b/g/n/ac + BT LE 4.2 combo embedded module, with ceramic SMT antennas on-board.

The M.2 Key B Slot can rely on an on-board microSIM slot.

The SBC-C43 offers an USB 3.0 Standard Type-A connector (combo with RJ-45 GbE connector), one USB 2.0 standard Type-A connector (combo with RJ-45 GbE connector), an internal USB 2.0 header and one USB 2.0 with OTG functionalities on micro-AB socket.

The audio functionalities of this board are realised by an I2S audio codec, which manages Line out and Mic In interfaces on a combo TRRS audio jack.

The standard functionalities of this board are then completed by 3x UART interfaces (RS-232, RS-485/RS-422, TTL level), an I2C interface, four A/D inputs, an SPI interface, 6x GPIOs and three CAN Bus interfaces.

The board is available both in commercial and in industrial temperature range.

Please refer to following chapter for a complete list of all peripherals integrated and characteristics. Not all combinations of these features are offered simultaneously; please visit SECO's website for a description of standard configuration modules offered. Configurations different from the standard offered must be evaluated singularly; please contact a SECO's sales representative / distributor for this.

## 2.2 Technical specifications

#### **Processors**

NXP i.MX 8 Family of processors, based on ARM® Cortex®-A72 Core + ARM® Cortex®-A53 Core + Cortex®-M4F core platform:

- i.MX 8 QuadMax: Dual A72-core, Quad A53-core, Dual M4F-core

- i.MX 8 QuadPlus: Single A72-core, Quad A53-core, Dual M4F-core

#### Memory

64-bit soldered down LPDDR4-1600 memory, up to 8GB total

### Graphics

2x Graphics accelerators Vivante GC7000/XVSX or GC7000Lite/XVSX (QuadMax and QuadPlus)

1x embedded VPU, supporting H.265(4K30) and H.264(1080p60) decoding and H.264 (1080p30) encoding

Supports 3 independent video outputs (total combined resolution 4K)

#### Video Interfaces

**OUTPUTS:**

HDMI 2.0a Tx interface

Optional eDP 1.4 interface

Optional Single/Dual-Channel 18-/24- bit LVDS interface

**INPUTS**:

HDMI 2.0a Rx interface

2x 4-lanes MIPI-CSI Camera interfaces

#### Video Resolution

HDMI: up to UltraHD (4K) LVDS, eDP: up to 1080p

### Mass Storage

eMMC 5.1 Drive soldered on-board, up to 64GB 1x S-ATA interface available on M.2 Socket 2 Key B Slot microSD Card Slot

4MB QuadSPI Flash NAND (boot device only)

### Networking

2x Gigabit Ethernet interfaces

Combo WiFi 802.11 a/b/g/n/ac + BT LE 4.2 module

M.2 Socket 2 Key B Slot for M.2 Modems

M.2 Socket1 Key E Slot for WiFi + BT external modules

#### USB

1 x USB 3.0 Host port on Type-A socket

1x USB 2.0 OTG port on micro-AB socket

1x USB 2.0 Host port on external Type-A socket

1x USB 2.0 Host port on internal connector

2 x USB 2.0 ports available on M.2 Key B and Key E slots

#### PCI-e

2x PCI-e x1 ports, available on M.2 Socket 1 Key E and on M.2 Socket 2 Key B

#### Audio

12S Audio Codec

HP + MIC combo TRRS audio connector

#### Serial Ports

1 x UART TTL

1 X RS-232 / UART TTL configurable

1 x RS-485 / RS-422 / UART TTL configurable

3x CAN interfaces

#### Other interfaces

4x Analog Inputs

6x GPIOs

SPI interface

12C interface

Embedded additional RTC circuitry for lowest power

consumption

SIM dedicated slot

Power supply voltage:  $+12V_{DC} \pm 10\%$

Operating temperature\*\*:  $0^{\circ}\text{C} \div +60^{\circ}\text{C}$  (commercial version)

-40°C ÷ +85°C (industrial version)

Dimensions: 146 x 102 mm (5,75" x 4,02")

## Supported Operating Systems:

Wind River Linux

Yocto Android

\*\* Measured at any point of SECO standard heatspreader for this product, during any and all times (including start-up). Actual temperature will widely depend on application, enclosure and/or environment. Upon customer to consider application-specific cooling solutions for the final system to keep the heatspreader temperature in the range indicated.

Please also check paragraph 4.1

## 2.3 Electrical specifications

SBC-C43 needs to be supplied only with an external  $12V_{DC} \pm 10\%$  power supply, with a minimal 60W power rating (SBC-C43 power consumption by itself is around 18W, more power is required for the possible attached devices).

This voltage can be supplied through a Right-angle connector type Molex Mini-Fit Jr, p/n 39-30-0040 or equivalent, with the pinout indicated in the table below.

| Power In Connector – CN38 |        |     |         |  |

|---------------------------|--------|-----|---------|--|

| Pin                       | Signal | Pin | Signal  |  |

| 1                         | GND    | 3   | VIN_SYS |  |

| 2                         | GND    | 4   | VIN_SYS |  |

## 2.3.1 Power available

When powering SBC-C43 with a PSU with characteristics greater or equal to the one described at beginning of previous paragraph, please consider well what is the typical scenario for using the board (i.e., which peripherals will be connected)

Since all the power must be supplied by an external PSU only, please balance well the typical final configuration, considering both the power consumption of the board itself and the power consumption of external devices.

This way it is possible to calculate preliminarily if a 60W PSU can be sufficient for system needing or if most powerful PSUs are required.

## 2.3.2 Power consumption

Using the following setup, the current consumption has been measured on +12VDC V<sub>IN</sub> power line.

- CPU: i.MX8 QuadMax

- 8GB LPDDR4

- 16GB eMMC onboard

- HDMI FHD display connected (no additional peripherals)

| Status                         | Average Value |        | Peak Value |        |

|--------------------------------|---------------|--------|------------|--------|

| Idle                           | 6.63W         | 0.55A  | 6.71W      | 0.56A  |

| OS Boot                        |               |        | 10.7W      | 0.891A |

| Video reproduction 1080p 60fps | 8.02W         | 0.668A | 8.51W      | 0.708A |

| Stress Test 1                  | 8.36W         | 0.696A | 9.29W      | 0.774A |

| Stress Test 2                  | 11.89W        | 0.99A  | 13.43W     | 1.119A |

| Stress Test 3                  | 13.06W        | 1.087A | 15.03W     | 1.251A |

| Stress Test 4                  | 17.37W        | 1.446A | 18.1W      | 1.507A |

## 2.3.3 RTC Battery

The SBC-C43 board can be equipped with an optional low-power Real Time Clock embedded on the module (which is a NXP PCF2123).

If the board is not equipped with the optional rechargeable battery, then it will be available a soldered horizontal 3V coin cell lithium battery to supply the RTC.

The battery used is a not-rechargeable CR1225 Lithium coin-cell battery, with a nominal capacity of 48mAh, , to supply such an RTC. The battery must be plugged on the onboard battery holder CN43.

In case of exhaustion, the battery should only be replaced with devices of the same type. Always check the orientation before inserting and make sure that they are aligned correctly and are not damaged or leaking.

Never allow the batteries to become short-circuited during handling.

! CAUTION: handling batteries incorrectly or replacing with not-approved devices may present a risk of fire or explosion.

Batteries supplied with SBC-C43 are compliant to requirements of European Directive 2006/66/EC regarding batteries and accumulators. When putting out of order SBC-C43, remove the batteries from the board in order to collect and dispose them according to the requirement of the same European Directive above mentioned. Even when replacing the batteries, the disposal has to be made according to these requirements.

## 2.3.4 Power rails naming convention

In all the tables contained in this manual, Power rails are named with the following meaning:

\_RUN: Switched voltages, i.e. power rails that are active only when the board is in ACPI's S0 (Working) state. Examples: +3.3V\_RUN, +5V\_RUN.

\_ALW: Always-on voltages, i.e. power rails that are active both in ACPI's S0 (Working), S3 (Standby) and S5 (Soft Off) state. Examples: +5V\_ALW, +3.3V\_ALW.

\_U: unswitched ACPI S3 voltages, i.e. power rails that are active both in ACPI's S0 (Working) and S3 (Standby) state. Examples: +1.5V\_U

Other suffixes are used for application specific power rails, which are derived from same voltage value of voltage switched rails, if it is not differently stated (for example, +5V<sub>HDMI</sub> is derived from +5V\_RUN, and so on).

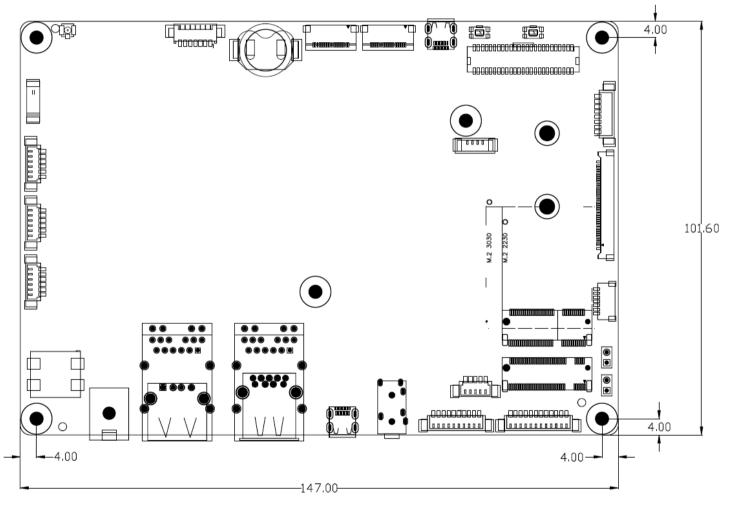

## 2.4 Mechanical specifications

Board dimensions are 146 x 102 mm (5,75" x 4,02").

The printed circuit of the board is made of ten layers, some of them are ground planes, for disturbance rejection.

## 2.5 Block diagram

## Chapter 3. CONNECTORS

- Introduction

- Connectors overview

- Connectors description

## 3.1 Introduction

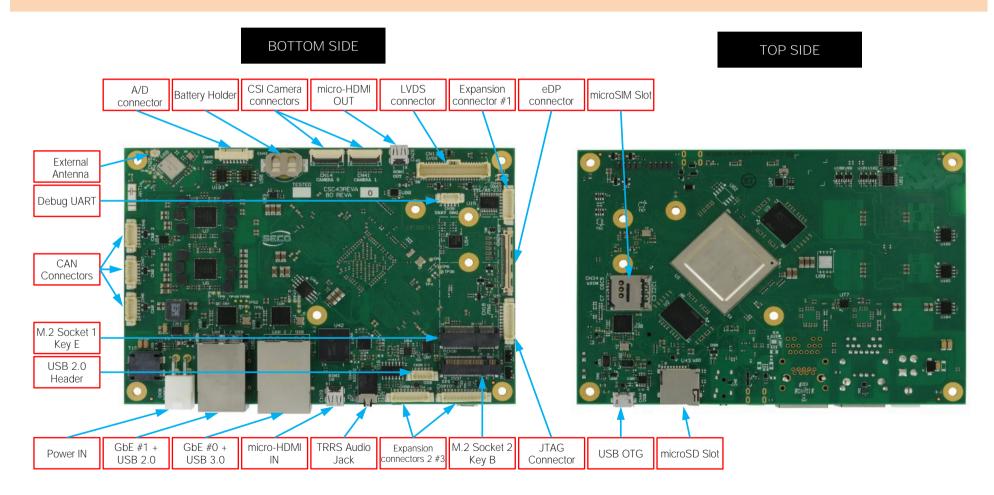

On SBC-C43 board, there are several connectors located on the upper plane. Standard connectors are placed on the same side of PCB, so that it is possible to place them on a panel of an eventual enclosure.

Please be aware that, depending on the configuration purchased, the appearance of the board can be significantly different from the following pictures.

## 3.2 Connectors overview

| Name | Description                     | Name | Description                      |

|------|---------------------------------|------|----------------------------------|

| CN14 | MIPI-CSI #0 Camera Connector    | CN43 | Battery Holder                   |

| CN17 | LVDS Connector                  | CN44 | USB 2.0 OTG micro-AB Connector   |

| CN18 | JTAG Connector                  | CN45 | A/D Header                       |

| CN20 | USB 2.0 internal header         | CN46 | CAN Bus #0 Connector             |

| CN21 | eDP Connector                   | CN47 | CAN Bus #1 Connector             |

| CN26 | External Antenna u.FL Connector | CN48 | CAN Bus #2 Connector             |

| CN28 | micro-HDMI Out Connector        | CN49 | Expansion connector #1           |

| CN29 | micro-HDMI In Connector         | CN50 | Expansion connector #2           |

| CN34 | microSIM card Slot              | CN51 | Expansion connector #3           |

| CN36 | M.2 Socket 1 Key E Slot         | CN52 | Combo GbE #1 + USB 2.0 connector |

| CN37 | M.2 Socket 2 Key B Slot         | CN53 | Combo GbE #0 + USB 3.0 connector |

| CN38 | Power In Connector              | U43  | microSD Slot                     |

| CN39 | Debug UART Connector            | SW1  | Reset Button                     |

| CN40 | TRRS Audio Jack                 | SW2  | Power Button                     |

| CN41 | MIPI-CSI #1 Camera Connector    |      |                                  |

#### Jumper List 3.2.1

| Name | Description | Name | Description |

|------|-------------|------|-------------|

| JP1  | SIM Detect  |      |             |

| JP2  | Boot Mode   |      |             |

|      |             |      |             |

## 3.3 Connectors description

#### 3.3.1 HDMI Connectors

|     | HDMI Out Connector – CN28 |     |           |  |  |

|-----|---------------------------|-----|-----------|--|--|

| Pin | Signal                    | Pin | Signal    |  |  |

| 1   | HPD                       | 2   |           |  |  |

| 3   | HDMI_TX2+                 | 4   | GND       |  |  |

| 5   | HDMI_TX2-                 | 6   | HDMI_TX1+ |  |  |

| 7   | GND                       | 8   | HDMI_TX1- |  |  |

| 9   | HDMI_TX0+                 | 10  | GND       |  |  |

| 11  | HDMI_TX0-                 | 12  | HMDI_CLK+ |  |  |

| 13  | GND                       | 14  | HDMI_CLK- |  |  |

| 15  | CEC                       | 16  | GND       |  |  |

| 17  | SCL                       | 18  | SDA       |  |  |

| 19  | +5V <sub>HDMI</sub>       |     |           |  |  |

NXP i.MX 8 family of processor has an embedded HDMI Tx module, which provides a HDMI standard interface for HDMI1.4 / 2.0a compliant displays.

For this reason, on SBC-C43 board there is the possibility of connecting directly one HDMI display, using a certified micro-HDMI connector (HDMI type D), CN28, type FCI p/n 10118242-001RLF.

Signals involved in HDMI Tx management are the following:

HMDI\_CLK+/HMDI\_CLK-: TMDS differential Clock.

HDMI TX0+/ HDMI TX0-: TMDS differential pair #0

HDMI TX1+/ HDMI TX1-: TMDS differential pair #1

HDMI\_TX2+/ HDMI\_TX2-: TMDS differential pair #2

SDA: DDC Data line for HDMI panel. Bidirectional signal, electrical level  $+5V_{HDMI}$  with a  $2k\Omega$  pull-up resistor.

SCL: DDC Clock line for HDMI panel. Output signal, electrical level  $+5V_{\text{HDMI}}$  with a  $2\text{k}\Omega$  pull-up resistor.

CEC: HDMI Consumer Electronics Control (CEC) Line. Bidirectional signal, electrical level  $+3.3V_RUN$  with a  $27k\Omega$  pull-up resistor.

HPD: Hot Plug Detect Input signal.  $+3.3V_RUN$  electrical level signal with  $1M\Omega$  pull-down resistor.

+5V<sub>HDMI</sub>: Power voltage reference for HDMI, directly derived from +5V\_RUN.

For ESD protection, on all data and voltage lines are placed clamping diodes for voltage transient suppression.

Always use HDMI-certified cables for the connection between the board and the HDMI display; a category 2 (High-Speed) cable is recommended for higher resolutions, category 1 cables can be used for 720p resolution.

|     | HDMI In Connector – CN29 |     |           |  |  |

|-----|--------------------------|-----|-----------|--|--|

| Pin | Signal                   | Pin | Signal    |  |  |

| 1   | HPD                      | 2   |           |  |  |

| 3   | HDMI_RX2+                | 4   | GND       |  |  |

| 5   | HDMI_RX2-                | 6   | HDMI_RX1+ |  |  |

| 7   | GND                      | 8   | HDMI_RX1- |  |  |

| 9   | HDMI_RX0+                | 10  | GND       |  |  |

| 11  | HDMI_RX0-                | 12  | HMDI_CLK+ |  |  |

| 13  | GND                      | 14  | HDMI_CLK- |  |  |

| 15  | CEC                      | 16  | GND       |  |  |

| 17  | SCL                      | 18  | SDA       |  |  |

| 19  | +5V <sub>SINK</sub>      |     |           |  |  |

NXP i.MX 8 family of processor also embeds an HDMI Rx module.

The same type of connector as CN28 is also used for HDMI Rx module, which supports HDCP2.0 and HDMI 1.4 external sources. HDMI IN connector CN29 is not available on all configurations, it is a factory option.

Signals involved in HDMI Rx management are the following:

HMDI\_CLK+/HMDI\_CLK-: TMDS differential Clock.

HDMI\_RXO+/ HDMI\_RXO-: TMDS differential pair #0

HDMI\_RX1+/ HDMI\_RX1-: TMDS differential pair #1

HDMI\_RX2+/ HDMI\_RX2-: TMDS differential pair #2

SDA: DDC Data line for HDMI panel. Bidirectional signal, electrical level  $+5V_{SINK}$  with a  $2k\Omega$  pull-up resistor.

SCL: DDC Clock line for HDMI panel. Output signal, electrical level  $+5V_{SINK}$  with a  $2k\Omega$  pull-up resistor.

CEC: HDMI Consumer Electronics Control (CEC) Line. Bidirectional signal, electrical level  $+3.3V_RUN$  with a  $27k\Omega$  pull-up resistor.

HPD: Hot Plug Detect Input signal. +3.3V\_RUN electrical level signal with  $1M\Omega$  pull-down resistor.

For ESD protection, on all data and voltage lines are placed clamping diodes for voltage transient suppression.

Always use HDMI-certified cables for the connection between the board and the HDMI display; a category 2 (High-Speed) cable is recommended for higher resolutions, category 1 cables can be used for 720p resolution.

<sup>+5</sup>V<sub>SINK</sub>: HDMI Input 5V Voltage reference.

#### 3.3.2 LVDS Connector

|     | LVDS + backlight Connector - CN17 |     |                 |  |  |

|-----|-----------------------------------|-----|-----------------|--|--|

| Pin | Signal                            | Pin | Signal          |  |  |

| 2   | LVDS_VCC_BKL_SW                   | 1   | LVDS_VCC_BKL_SW |  |  |

| 4   | LVDS_VCC_LCD_SW                   | 3   | +3.3V_RUN       |  |  |

| 6   | LVDS_VCC_LCD_SW                   | 5   | LVDS_TS_SCL     |  |  |

| 8   | GND                               | 7   | GND             |  |  |

| 10  | LVDS0_TX0+                        | 9   | LVDS_TS_SDA     |  |  |

| 12  | GND                               | 11  | GND             |  |  |

| 14  | LVDS0_TX1+                        | 13  | LVDS0_TX1-      |  |  |

| 16  | GND                               | 15  | GND             |  |  |

| 18  | LVDS0_TX2+                        | 17  | LVDS0_TX2-      |  |  |

| 20  | GND                               | 19  | GND             |  |  |

| 22  | LVDS0_TX3+                        | 21  | LVDS0_TX3-      |  |  |

| 24  | GND                               | 23  | GND             |  |  |

| 26  | LVDS0_CLK+                        | 25  | LVDS0_CLK-      |  |  |

| 28  | LVDS_BKL_PWM                      | 27  | LVDS_BKL_ANA    |  |  |

| 30  | LVDS_PANEL_ON                     | 29  | DISPLAY_BKL_ON  |  |  |

| 32  | LVDS_TS_INT#                      | 31  | LVDS_TS_RST     |  |  |

| 34  | LVDS1_TX0+                        | 33  | LVDS1_TX0-      |  |  |

| 36  | GND                               | 35  | GND             |  |  |

| 38  | LVDS1_TX1+                        | 37  | LVDS1_TX1-      |  |  |

| 40  | GND                               | 39  | GND             |  |  |

| 42  | LVDS1_TX2+                        | 41  | LVDS1_TX2-      |  |  |

| 44  | GND                               | 43  | GND             |  |  |

| 46  | LVDS1_TX3+                        | 45  | LVDS1_TX3-      |  |  |

| 48  | GND                               | 47  | GND             |  |  |

| 50  | LVDS1_CLK+                        | 49  | LVDS1_CLK+      |  |  |

|     |                                   |     |                 |  |  |

In addition to HDMI, SBC-C43 board can be interfaced to LCD displays using its LVDS interface, which allows the connection of displays with a colour depth of 18 or 24 bit, single or dual channel.

For the connection, a connector type HR A1014WV-S-2X25P or equivalent (2 x 25p, male, straight, P1, low profile, polarized) is provided, with the pin-out shown in the table below.

Mating connector: HR A1014H -2X25P with HR A1014-T female crimp terminals.

Alternative mating connector, MOLEX 501189-5010 with crimp terminals series 501334.

On the same connectors, are also implemented signals for direct driving of display's backlight: power voltages for LCD and backlight (LVDS\_VCC\_BKL\_SW and LVDS VCC LCD SW) and control signals (Backlight enable signal, LVDS BKL EN, LCD enable signal, LVDS VDD EN, PWM and Analog Backlight Brightness Control signal, LVDS BKL PWM and LVDS BKL ANA).

The LCD software-driven voltage, i.e. signal LVDS VCC LCD SW, can be factory regulated to be connected to +5V ALW or +3.3V ALW, while backlight software-driven voltage, i.e. signal LVDS VCC BKL SW, can be factory regulated to be connected to +5V ALW or +12V ALW

These are factory configurations, please take care of specifying which is the configuration needed for LVDS VCC LCD SW and LVDS VCC BKL SW voltage rail.

When building a cable for connection of LVDS displays, please take care of twist as tight as possible differential pairs' signal wires, in order to reduce EMI interferences. Shielded cables are also recommended. Here following the signals related to LVDS management:

LVDS0\_TX0+/LVDS0\_TX0-: LVDS Channel #0 differential data pair #0.

LVDS0 TX1+/LVDS0 TX1-: LVDS Channel #0 differential data pair #1.

LVDS0\_TX2+/LVDS0\_TX2-: LVDS Channel #0 differential data pair #2.

LVDSO\_TX3+/LVDSO\_TX3-: LVDS Channel #0 differential data pair #3.

LVDS0\_CLK+/LVDS0\_CLK-: LVDS Channel #0 differential Clock.

LVDS1 TX0+/LVDS1 TX0-: LVDS Channel #1 differential data pair #0.

LVDS1 TX1+/LVDS1 TX1-: LVDS Channel #1 differential data pair #1.

LVDS1 TX2+/LVDS1 TX2-: LVDS Channel #1 differential data pair #2.

25

LVDS1\_TX3+/LVDS1\_TX3-: LVDS Channel #1 differential data pair #3.

LVDS1\_CLK+/LVDS1\_CLK-: LVDS Channel #1 differential Clock.

LVDS\_VCC\_BKL\_SW: Backlight Power rail, connected to +12V\_ALW through a power switch.

LVDS\_VCC\_LCD\_SW: LCD Power rail, connected to +3.3V\_ALW through a power switch.

LVDS\_BKL\_ANA: Backlight analog dimming signal, electrical level +5V\_ALW.

LVDS\_BKL\_PWM: this signal can be used to adjust the backlight brightness in displays supporting Pulse Width Modulated (PWM) regulations (electrical level LVDS\_VCC\_LCD\_SW with a  $10 \text{k}\Omega$  pull-up resistor).

LVDS\_PANEL\_ON: LCD Panel enable signal, electrical level to LVDS\_VCC\_LCD\_SW with 10kΩ pull-up resistor.

DISPLAY\_BKL\_ON: Backlight enable signal, electrical level to LVDS\_VCC\_LCD\_SW with 10kΩ pull-up resistor.

LVDS\_TS\_SCL: Touchscreen I2C Bus data line. Bidirectional signal, electrical level  $+3.3V_RUN$  with a  $2K2\Omega$  pull-up resistor.

LVDS\_TS\_SDA: Touchscreen I2C Bus clock line. Output signal, electrical level +3.3V\_RUN with a 2K2Ω pull-up resistor.

LVDS\_TS\_INT#: +3.3V\_RUN electrical level input with a 100k pull-up resistor. This signal can be used to serve the interrupt request of an eventual external Touch Screen connected to the dedicated I2C interface.

LVDS\_TS\_RST: +3.3V\_RUN electrical level output with a 100KΩ pull-down resistor. This signal can be used to drive a reset of an eventual external Touch Screen connected to the dedicated I2C interface.

#### 3.3.3 eDP Connector

|                      | 55             |     | ONO            |  |  |

|----------------------|----------------|-----|----------------|--|--|

| eDP connector - CN21 |                |     |                |  |  |

| Pin                  | Signal         | Pin | Signal         |  |  |

| 1                    |                | 21  | EDP_VCC_LCD_SW |  |  |

| 2                    | EDP_VCC_BKL_SW | 22  | EDP_VCC_LCD_SW |  |  |

| 3                    | EDP_VCC_BKL_SW | 23  | EDP_VCC_LCD_SW |  |  |

| 4                    | EDP_VCC_BKL_SW | 24  | GND            |  |  |

| 5                    | EDP_VCC_BKL_SW | 25  | eDP_AUX_N      |  |  |

| 6                    |                | 26  | eDP_AUX_P      |  |  |

| 7                    |                | 27  | GND            |  |  |

| 8                    | eDP_BKL_CTRL   | 28  | eDP_ML0P       |  |  |

| 9                    | eDP_BKL_ON     | 29  | eDP_MLON       |  |  |

| 10                   | GND            | 30  | GND            |  |  |

| 11                   | GND            | 31  | eDP_ML1P       |  |  |

| 12                   | GND            | 32  | eDP_ML1N       |  |  |

| 13                   | GND            | 33  | GND            |  |  |

| 14                   | eDP_HPD        | 34  | eDP_ML2P       |  |  |

| 15                   | GND            | 35  | eDP_ML2N       |  |  |

| 16                   | GND            | 36  | GND            |  |  |

| 17                   | GND            | 37  | eDP_ML3P       |  |  |

| 18                   | GND            | 38  | eDP_ML3N       |  |  |

| 19                   |                | 39  | GND            |  |  |

| 20                   | EDP_VCC_LCD_SW | 40  |                |  |  |

|                      |                |     |                |  |  |

SBC-C43 offers an optional dedicated embedded Display Port interface.

This interface is realized through Texas Instrument SN65DSl86 MIPI $^{\circ}$  DSI to eDP $^{\intercal M}$  bridge, connected from one channel of the four-lane MIPI display serial interface to eDP interface of the VESA connector.

For the connection of this kind of displays, on-board there is a VESA® certified connectors for embedded Display Port interface, type STARCONN p/n 300E40-0110RA-G3 or equivalent (microcoaxial cable connector, 0.5mm pitch, 40 positions).

On this connector, EDP\_VCC\_BKL\_SW and EDP\_VCC\_LCD\_SW are the software-enabled voltage rails that can be used to supply the LCD and related Backlight Unit.

The LCD software-driven voltage, i.e. signal EDP\_VCC\_LCD\_SW, can be factory regulated to be connected to +5V\_ALW or +3.3V\_ALW, while backlight software-driven voltage, i.e. signal EDP\_VCC\_BKL\_SW, can be factory regulated to be connected to +5V\_ALW or +12V\_ALW

These are factory configurations, please take care of specifying which is the configuration needed for EDP\_VCC\_LCD\_SW and EDP\_VCC\_BKL\_SW voltage rail.

Here following the signals involved in eDP management:

eDP\_MLOP/eDP\_MLON: embedded DP differential data pair #0.

eDP ML1P/eDP ML1N: embedded DP differential data pair #1.

eDP\_ML2P/eDP\_ML2N: embedded DP differential data pair #2.

eDP ML3P/eDP ML3N: embedded DP differential data pair #3.

eDP\_AUXN/eDP\_AUXP: embedded DP auxiliary channel differential data pair.

eDP\_HPD: embedded DP Hot Plug Detect. +3.3V\_RUN electrical level signal.

eDP\_BKL\_CTRL: this signal can be used to adjust the backlight brightness in displays supporting Pulse Width Modulated (PWM) regulations, electrical level +3.3V\_RUN.

eDP\_BKL\_ON: Backlight enable signal, electrical level +3.3V\_RUN.

#### 3.3.4 CSI Camera Connectors

SBC-C43 with NXP iMX8 Processor includes an Image Processing Subsystem, that can be used for video applications, like video-preview, video recording and frame grabbing. It is possible to access to the two embedded video input ports through as many FFC/FPC optional connectors, type OMRON p/n XF2M-1815-1A which are able to accept 18 poles 0.5mm pitch FFC cables.

The pinout of these connector is shown in the tables below. All CSI differential pairs are managed by i.MX8 CSI Host Controller's Camera Input #0 and #1.

| CSI Camera Connector #0 - CN14 |            |     |                    |  |

|--------------------------------|------------|-----|--------------------|--|

| Pin                            | Signal     | Pin | Signal             |  |

| 1                              | CSI_P0_DN3 | 10  | CSI_P0_DN0         |  |

| 2                              | CSI_P0_DP3 | 11  | CSI_P0_DP0         |  |

| 3                              | CSI_P0_DN2 | 12  | GND                |  |

| 4                              | CSI_P0_DP2 | 13  | MIPI_CSIO_PWDN     |  |

| 5                              | CSI_P0_DN1 | 14  | MIPI_CSIO_MCKL_OUT |  |

| 6                              | CSI_P0_DP1 | 15  | MIPI_CSI0_I2C0_SCL |  |

| 7                              | CSI_PO_CKN | 16  | MIPI_CSI0_I2C0_SDA |  |

| 8                              | CSI_P0_CKP | 17  | MIPI_CSIO_RST_B    |  |

| 9                              | GND        | 18  | +3.3V_RUN          |  |

Here following signal related to Camera Input #0:

CSI\_P0\_DP0 / CSI\_P0\_DN0: CSI2 Camera serial input, Receiving Input Differential pair #0.

CSI\_P0\_DP1 / CSI\_P0\_DN1: CSI2 Camera serial input, Receiving Input Differential pair #1.

CSI PO DP2 / CSI PO DN2: CSI2 Camera serial input, Receiving Input Differential pair #2.

CSI\_P0\_DP3 / CSI\_P0\_DN3: CSI2 Camera serial input, Receiving Input Differential pair #3.

CSI PO CKP / CSI PO CKN: CSI Camera, Clock input differential pair.

MIPI\_CSIO\_PWDN: External camera module Power down signal. It is an active high signal with electrical level +1.8V RUN.

MIPI\_CSIO\_MCKL\_OUT: Master Clock, it is managed by CSI Host Controller. It is suggested, however, to use camera modules with onboard crystal / oscillator, and avoid using this signal. Indeed, it could cause problems for EMI compliance requirements.

MIPI\_CSI0\_I2C0\_SCL: general purpose I2C Bus clock line. Output signal, electrical level +1.8V RUN with a  $2k2\Omega$  pull-up resistor.

MIPI\_CSIO\_I2CO\_SDA: general purpose I2C Bus data line. Bidirectional signal, electrical level

MIPI\_CSIO\_RST\_B: External camera module reset signal output, it is an active low signal.

| CSI Camera Connector #1 – CN41 |            |     |                |

|--------------------------------|------------|-----|----------------|

| Pin                            | Signal     | Pin | Signal         |

| 1                              | CSI_P1_DN3 | 10  | CSI_P1_DN0     |

| 2                              | CSI_P1_DP3 | 11  | CSI_P1_DP0     |

| 3                              | CSI_P1_DN2 | 12  | GND            |

| 4                              | CSI_P1_DP2 | 13  | MIPI_CSI1_PWDN |

Here following signal related to Camera Input #1:

CSI\_P1\_DP0 / CSI\_P1\_DN0: CSI2 Camera serial input, Receiving Input Differential pair #0.

CSI\_P1\_DP1 / CSI\_P1\_DN1: CSI2 Camera serial input, Receiving Input Differential pair #1.

CSI\_P1\_DP2 / CSI\_P1\_DN2: CSI2 Camera serial input, Receiving Input Differential pair #2.

CSI\_P1\_DP3 / CSI\_P1\_DN3: CSI2 Camera serial input, Receiving Input Differential pair #3.

CSI\_P1\_CKP / CSI\_P1\_CKN: CSI Camera, Clock input differential pair.

MIPI\_CSI1\_PWDN: External camera module Power enable signal. It is an active high signal with electrical level +1.8V\_RUN.

<sup>+1.8</sup>VRUN with a  $2k2\Omega$  pull-up resistor.

| 5 | CSI_P1_DN1 | 14 | MIPI_CSI1_MCKL_OUT |

|---|------------|----|--------------------|

| 6 | CSI_P1_DP1 | 15 | MIPI_CSI1_I2C0_SCL |

| 7 | CSI_P1_CKN | 16 | MIPI_CSI1_I2C0_SDA |

| 8 | CSI_P1_CKP | 17 | MIPI_CSI1_RST_B    |

| 9 | GND        | 18 | +3.3V_RUN          |

MIPI\_CSI1\_MCKL\_OUT: Master Clock, it is managed by CSI Host Controller. It is suggested, however, to use camera modules with onboard crystal / oscillator, and avoid using this signal. Indeed, it could cause problems for EMI compliance requirements.

MIPI\_CSI1\_I2CO\_SCL: general purpose I2C Bus clock line. Output signal, electrical level  $+1.8V_RUN$  with a  $2k2\Omega$  pull-up resistor.

MIPI\_CSI1\_I2C0\_SDA: general purpose I2C Bus data line. Bidirectional signal, electrical level  $+1.8V_RUN$  with a  $2k2\Omega$  pull-up resistor.

MIPI\_CSIO\_RST\_B: External camera module reset signal output, it is an active low signal.

## 3.3.5 TRSS Audio jack

On SBC-C43 board, audio functionalities are controlled by an I2S Audio Codec type TLV320AIC3204IRHBR.

| TRRS Audio jack- CN40 |                             |  |  |

|-----------------------|-----------------------------|--|--|

| Pin                   | Signal                      |  |  |

| TIP                   | Headphone Out Left Channel  |  |  |

| RING1                 | Headphone Out Right Channel |  |  |

| RING2                 | GND                         |  |  |

| SLEEVE                | MIC_IN                      |  |  |

It is possible to have Stereo Line Out and Mic In Audio functionalities, all of them on a single TRRS Combo Audio Jack, i.e. a single jack which offer both stereo Line Out and Mic In functionalities.

Such TRRS Combo Audio jack can be used with any 4-poles 3.5mm diameter audio jack, with pinout compatible with the most recent Headsets, shown in the table on the left.

## 3.3.6 Gigabit Ethernet + USB Connectors

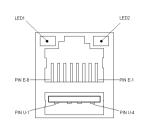

On SBC-C43 board it is possible to have up to two Gigabit Ethernet connectors, managed using as many DP83867CR GbE Transceivers. Each one of these optional connections is available on a combo connector, where the GbE interface is coupled to an USB interface.

More specifically, on connector CN52, type TRXCOM p/n TRJU3836B81N, with 2kV decoupling capacitors, it is available GbE LAN port #1 along with USB 2.0 downstream port #3, managed by the USB HSIC Hub.

| Combo GbE #1 + USB 2.0 connector - CN52 |                     |  |  |

|-----------------------------------------|---------------------|--|--|

| Pin                                     | Signal              |  |  |

| U1                                      | +5V <sub>USB3</sub> |  |  |

| U2                                      | USB_P3-             |  |  |

| U3                                      | USB_P3+             |  |  |

| U4                                      | GND                 |  |  |

| E1                                      | ETH1_MDI0+          |  |  |

| E2                                      | ETH1_MDI0-          |  |  |

| E3                                      | ETH1_MDl1+          |  |  |

| E4                                      | ETH1_MDI2+          |  |  |

| E5                                      | ETH1_MDI2-          |  |  |

| E6                                      | ETH1_MDI1-          |  |  |

| E7                                      | ETH1_MDI3+          |  |  |

| E8                                      | ETH1_MDI3-          |  |  |

Signals description:

USB\_P3+/USB\_P3-: USB Port #3 differential pair; it is managed by Microchip USB4604 Hub controller's Downstream Port #3.

+5V<sub>USB3</sub> voltage is derived from +5V\_ALW power rail using a 600mA power switch.

ETH1\_MDI0+/ETH1\_MDI0-: Ethernet Controller Media Dependent Interface (MDI) I/O differential pair #0. It is the first differential pair in Gigabit Ethernet mode, and the Transmit differential pair in 10/100 Mbps modes.

ETH1\_MDI1+/ ETH1\_MDI1-: Ethernet Controller Media Dependent Interface (MDI) I/O differential pair #1. It is the second differential pair in Gigabit Ethernet mode, and the Receive differential pair in 10/100 Mbps modes.

ETH1\_MDI2+/ ETH1\_MDI2-: Ethernet Controller Media Dependent Interface (MDI) I/O differential pair #2. It is the third differential pair in Gigabit Ethernet mode; it is not used in 10/100Mbps modes.

ETH1\_MDI3+/ ETH1\_MDI3-: Ethernet Controller Media Dependent Interface (MDI) I/O differential pair #3. It is the fourth differential pair in Gigabit Ethernet mode; it is not used in 10/100Mbps modes.

On the connector there are also two LEDs for each port. Left LED is bicolor (Orange / Green) and shows 10/100 or 1000 connection: orange means 100Mbps connection, green means 1000Mpbs connection, when the LED is Off then 10Mpbs or no connection is available. The right

LED is Yellow and shows ACTIVITY presence.

This interface is compatible both with Gigabit Ethernet (1000Mbps) and with Fast Ethernet (10/100Mbps) Networks. It will configure automatically to work with the existing network.

Please be aware that they will work in Gigabit mode only in case that they are connected to Gigabit Ethernet switches/hubs/routers. For the connection, cables category Cat5e or better are required. Cables category Cat6 are recommended for noise reduction and EMC compatibility issues, especially when the length of the cable is significant.

Instead on connector CN53, type TRXCOM p/n TRJU3636B81NL, with 2kV decoupling capacitors, it is available GbE LAN port #0 along with USB 3.0 port #3, directly managed by the i.MX8 processor.

| Combo GbE #0 + USB 3.0 connector - CN53 |                    |  |

|-----------------------------------------|--------------------|--|

| Pin                                     | Signal             |  |

| U1                                      | +5V <sub>USB</sub> |  |

| U2                                      | USB_H1-            |  |

| U3                                      | USB_H1+            |  |

| U4                                      | GND                |  |

| U5                                      | USB_SSRX1-         |  |

| U6                                      | USB_SSRX1+         |  |

| U7                                      | GND                |  |

| U8                                      | USB_SSTX1-         |  |

| U9                                      | USB_SSTX1+         |  |

| E1                                      | ETHO_MDIO+         |  |

| E2                                      | ETHO_MDIO-         |  |

| E3                                      | ETHO_MDI1+         |  |

| E4                                      | ETHO_MDI2+         |  |

| E5                                      | ETHO_MDI2-         |  |

| E6                                      | ETHO_MDI1-         |  |

| E7                                      | ETHO_MDI3+         |  |

| E8                                      | ETHO_MDI3-         |  |

Signals description:

USB\_H1+/USB\_H1-: USB 2.0 Host Port #1 differential pair;

USB\_SSRX1+/USB\_SSRX1-: USB Super Speed Port #1 receive differential pair; USB\_SSTX1+/USB\_SSTX1-: USB Super Speed Port #1 transmit differential pair;

+5VUSB voltage is derived from +5V ALW power rail using a 1A power switch.

Common mode chokes are placed on all USB differential pairs for EMI compliance. For ESD protection, on all data and voltage lines are placed clamping diodes for voltage transient suppression.

ETHO\_MDIO+/ETH1\_MDIO-: Ethernet Controller Media Dependent Interface (MDI) I/O differential pair #0. It is the first differential pair in Gigabit Ethernet mode, and the Transmit differential pair in 10/100 Mbps modes.

ETHO\_MDI1+/ ETH1\_MDI1-: Ethernet Controller Media Dependent Interface (MDI) I/O differential pair #1. It is the second differential pair in Gigabit Ethernet mode, and the Receive differential pair in 10/100 Mbps modes.

ETHO\_MDI2+/ ETH1\_MDI2-: Ethernet Controller Media Dependent Interface (MDI) I/O differential pair #2. It is the third differential pair in Gigabit Ethernet mode; it is not used in 10/100Mbps modes.

ETHO\_MDI3+/ ETH1\_MDI3-: Ethernet Controller Media Dependent Interface (MDI) I/O differential pair #3. It is the fourth differential pair in Gigabit Ethernet mode; it is not used in 10/100Mbps modes.

On the connector there are also two LEDs for each port. Left LED is bicolor (Orange / Green) and shows 10/100 or 1000 connection: orange means 100Mbps connection, green means 1000Mpbs connection, when the LED is Off then 10Mpbs or no connection is available. The right LED is Yellow and shows ACTIVITY presence.

This interface is compatible both with Gigabit Ethernet (1000Mbps) and with Fast Ethernet (10/100Mbps) Networks. It will configure automatically to work with the existing network.

Please be aware that they will work in Gigabit mode only in case that they are connected to Gigabit Ethernet switches/hubs/routers. For the connection, cables category Cat5e or better are required. Cables category Cat6 are recommended for noise reduction and EMC compatibility issues, especially when the length of the cable is significant.

#### 3.3.7 USB Connectors

On SBC-C43 board there are two USB ports directly available on external connectors.

| USB 2.0 Internal Header – CN20 |                     |  |  |

|--------------------------------|---------------------|--|--|

| Pin                            | Signal              |  |  |

| 1                              | +5V <sub>USB4</sub> |  |  |

| 2                              | USB_P4-             |  |  |

| 3                              | USB_P4+             |  |  |

| 4                              | GND                 |  |  |

| 5                              | SHLD (GND)          |  |  |

The USB downstream port #4 managed by the USB HSIC Hub is available on a 5-pin p1.27mm connector type Molex p/n 53398-0571 or equivalent, with pinout shown in the table on the left.

Mating connector: MOLEX 51021-0500 receptacle with 50079-8000 female crimp terminals.

Signal Description of this port:

USB\_P4+/USB\_P4-: USB Port #4 differential pair; it is managed by Microchip USB4604 Hub controller's Downstream Port #4.

+5V<sub>USB4</sub> voltage is derived from +5V\_ALW power rail using a 600mA power switch.

## USB micro-AB connector - CN44

| USB IIIICIO-AB COIIIIeCIOI — CIN44 |            |  |

|------------------------------------|------------|--|

| Pin                                | Signal     |  |

| 1                                  | USB_VBUS   |  |

| 2                                  | USB_OTG_D- |  |

| 3                                  | USB_OTG_D+ |  |

| 4                                  | USB_ID     |  |

| 5                                  | SHLD (GND) |  |

In addition, there is an USB OTG Port, managed directly by the i.MX8 processor, which is carried to a standard micro-AB connector, described in the table on the left.

Depending on the needed use of the system, it is necessary to connect micro-A or micro-B USB cables to connector CN44

A micro-A USB cable has to be used when the system has to work in Host mode. In this case, USB\_VBUS is a power output of SBC-C43 Board for the connected device.

When a micro-B USB cable is used, its USB\_ID pin is floating; this way, the board acknowledges that it must configure itself to work as a Client. In this case, USB\_VBUS is an input of the carrier board from the external Host.

Signal description of this port:

USB\_OTG\_D+/USB\_OTG\_D-: USB OTG Port #1 differential pair.

USB\_VBUS: USB voltage rail. It is an input for USB port working in Client mode, an output for Host mode.

USB\_ID: Client/Host identification signal. This signal is high when the USB port works in client mode, is low when works in Host mode.

## 3.3.8 M.2 2230 Socket 1 Key E Connectivity Slot

| M.2 Connectivity Slot (Socket 1 Key E type 2230) – CN36 |                 |     |           |  |

|---------------------------------------------------------|-----------------|-----|-----------|--|

| Pin                                                     | Signal          | Pin | Signal    |  |

| 1                                                       | GND             | 2   | +3.3V_RUN |  |

| 3                                                       | USB_P2+         | 4   | +3.3V_RUN |  |

| 5                                                       | USB_P2-         | 6   |           |  |

| 7                                                       | GND             | 8   |           |  |

| 9                                                       |                 | 10  |           |  |

| 11                                                      |                 | 12  |           |  |

| 13                                                      |                 | 14  |           |  |

| 15                                                      |                 | 16  |           |  |

| 17                                                      |                 | 18  | GND       |  |

| 19                                                      |                 | 20  |           |  |

| 21                                                      |                 | 22  |           |  |

| 23                                                      |                 |     |           |  |

|                                                         |                 | 32  |           |  |

| 33                                                      | GND             | 34  |           |  |

| 35                                                      | PCle1_Tx0-      | 36  |           |  |

| 37                                                      | PCle1_Tx0+      | 38  |           |  |

| 39                                                      | GND             | 40  |           |  |

| 41                                                      | PCle1_Rx0-      | 42  |           |  |

| 43                                                      | PCle1_Rx0+      | 44  |           |  |

| 45                                                      | GND             | 46  |           |  |

| 47                                                      | PCIe_KEYE_CLK+  | 48  |           |  |

| 49                                                      | PCIe_ KEYE_CLK- | 50  |           |  |

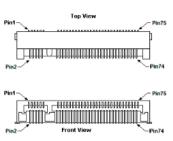

It is possible to increase the connectivity of the SBC-C43 board by using M.2 Socket 1 Key E connectivity slot.

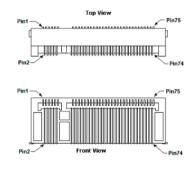

The connector used for the M.2 Connectivity slot is CN36, which is a standard 75 pin M.2 Key E connector, type LOTES p/n APCl0076-P001A, H=4.2mm, with the pinout shown in the table on the left.

On the SBC-C43 board there is also a Threaded Spacer which allows the placement of M.2 Socket 1 Key E connectivity modules in 2230 size.

| 51 | GND           | 52 | PCIE_RST1#          |

|----|---------------|----|---------------------|

| 53 | CLK_REQ1#     | 54 | M2_KEYE_W_DIS2#     |

| 55 | PCIe_WAKE1#   | 56 | M2_KEYE_W_DIS1#     |

| 57 | GND           | 58 | M.2_KeyE_I2C_SDA    |

| 59 |               | 60 | M.2_KeyE_I2C_SCL    |

| 61 |               | 62 | M.2_KeyE_I2C_ALERT# |

| 63 | M2_KEYE_PRST# | 64 |                     |

| 65 |               | 66 |                     |

| 67 |               | 68 |                     |

| 69 | GND           | 70 |                     |

| 71 |               | 72 | +3.3V_RUN           |

| 73 |               | 74 | +3.3V_RUN           |

| 75 | GND           |    |                     |

## Signal Description

USB\_P2+ / USB\_P2-: USB Port #2 differential pair; it is managed by Microchip USB4604 Hub controller's Downstream Port #2.

PCle1\_Tx+/PCle1\_Tx-: PCl Express lane #1, Transmitting Output Differential pair PCle1\_Rx+/PCle1\_Rx-: PCl Express lane #1, Receiving Input Differential pair PCle\_KEYE\_CLK+/ PCle\_KEYE\_CLK-: PCl Express Reference Clock for lane #1, Differential

#### Pair

PCIe\_WAKE1#: Board's Wake Input, it must be externally driven by the module inserted in the slot when it requires waking up the system. Active low signal, electrical level  $+3.3V_RUN$  with a  $47K\Omega$  pull-up resistor

CLK\_REQ1#: PCI-e Clock Request Input. Active low signal, electrical level +3.3V\_RUN with a 47K\O pull-up resistor. This signal shall be driven low by any module inserted in the connectivity slot, in order to ensure that the SoC makes available the reference clock.

PCIE\_RST1#: Reset Signal that is sent from the SoC to all PCI-e devices available on the board. It is a +3.3V\_RUN active-low signal with 100kΩ pull-down.

KEYE\_W\_DISABLE1#: M.2 Key E Wireless module functionality disable signal #1, active low signal

KEYE\_W\_DISABLE2#: M.2 Key E Wireless module functionality disable signal #2, active low signal

M.2\_KeyE\_I2C\_SDA: I2C Bus data line. Bidirectional signal, electrical level +1.8V\_RUN with a 2K2Ω pull-up resistor.

M.2\_KeyE\_I2C\_SCL: I2C Bus clock line. Bidirectional signal, electrical level +1.8V\_RUN with a 2K2Ω pull-up resistor.

M.2\_KeyE\_I2C\_ALERT#: I2C Bus Alert. Input signal, electrical level +1.8V\_RUN with a 2K2Ω pull-up resistor.

M2\_KEYE\_PRST#: M.2 Key E input for detection when a module is inserted in the slot. Active low signal, electrical level  $+3.3V_RUN$  with a  $100K\Omega$  pull-up resistor.

## 3.3.9 M.2 SSD/WWAN Slot: Socket 2 Key B

| M.2 SSD/WWAN Slot (Socket 2 Key B type 3042/2260- CN37) |            |     |                 |  |

|---------------------------------------------------------|------------|-----|-----------------|--|

| Pin                                                     | Signal     | Pin | Signal          |  |

| 1                                                       | CONFIG3    | 2   | +3.3V_RUN       |  |

| 3                                                       | GND        | 4   | +3.3V_RUN       |  |

| 5                                                       | GND        | 6   | M2_KEYB_PWROFF# |  |

| 7                                                       | USB_P1-    | 8   | M2_KEYB_W_DIS1# |  |

| 9                                                       | USB_P1+    | 10  |                 |  |

| 11                                                      | GND        | 20  |                 |  |

| 21                                                      | CONF0      | 22  |                 |  |

| 23                                                      |            | 24  |                 |  |

| 25                                                      |            | 26  | M2_KEYB_W_DIS2# |  |

| 27                                                      | GND        | 28  |                 |  |

| 29                                                      | PCle0_Rx1- | 30  | UIM_RESET       |  |

The mass storage capabilities of the SBC-C43 board are completed by an M.2 SSD Slot, which allow plugging M.2 Socket 2 Key B Solid State Drives.

The same slot can be used alternatively for the connection of Connectivity modules, using PCI-e x2 interface or USB 2.0 interface (USB interface is always available, while SATA interface is alternative to PCI-e interface).

The connector used for the M.2 SSD slot is CN37, which is a standard 75 pin M.2 Key B connector, type LOTES p/n APCI0087-P001A, H=8.5mm, with the pinout shown in the table on the left.

On the SBC-C43 board there is also a Threaded Spacer which allows the placement of M.2 Socket 2 Key B SSD modules in 2260 size.

It is possible to place also modules in 2242 / 3042 size, by using a M/F Spacer which allow fixing the M.2 SSD on the spacer already available on the PCB, deemed for the fixing of the M.2 connectivity slot (see previous paragraph).

Here following the signals related to the SATA interface:

SATAO\_TX+/SATAO\_TX-: Serial ATA Channel #0 Transmit differential pair

| 31 | PCle0_Rx1+           | 32 | UIM_CLK     |

|----|----------------------|----|-------------|

| 33 | GND                  | 34 | UIM_DATA    |

| 35 | PCle0_Tx1-           | 36 | UIM_PWR     |

| 37 | PCle0_Tx1+           | 38 |             |

| 39 | GND                  | 40 |             |

| 41 | PCle0_Rx0-/SATA0_RX+ | 42 |             |

| 43 | PCle0_Rx0+/SATA0_RX- | 44 |             |

| 45 | GND                  | 46 |             |

| 47 | PCle0_Tx0-/SATA0_TX- | 48 |             |

| 49 | PCle0_Tx0+/SATA0_TX+ | 50 | PCIE_RST0#  |

| 51 | GND                  | 52 | CLK_REQ0#   |

| 53 | PCle_KEYB_CLK+       | 54 | PCIe_WAKE0# |

| 55 | PCle_KEYB_CLK-       | 56 |             |

| 57 | GND                  | 58 |             |

| 59 |                      | 60 |             |

| 61 |                      | 62 |             |

| 63 |                      | 64 |             |

| 65 |                      | 66 | SIM_DETECT  |

| 67 |                      | 68 |             |

| 69 | CONF1                | 70 | +3.3V_RUN   |

| 71 | GND                  | 72 | +3.3V_RUN   |

| 73 | GND                  | 74 | +3.3V_RUN   |

| 75 | CONF2                |    |             |

|    |                      |    |             |

SATAO RX+/SATAO RX-: Serial ATA Channel #0 Receive differential pair

10nF AC series decoupling capacitors are placed on each line of SATA differential pairs.

Here following the signals related to the PCI-e interface:

PCIeO\_TxO+/PCIeO\_TxO-: PCI Express port #0 lane #0, Transmitting Output Differential pair

PCle0\_Rx0+/PCle0\_Rx0-: PCl Express port #0 lane #0, Receiving Input Differential pair

PCleO\_Tx1+/PCleO\_Tx1-: PCl Express port #0 lane #1, Transmitting Output Differential pair

PCle0\_Rx1+/PCle0\_Rx1-: PCl Express port #0 lane #1, Receiving Input Differential pair

PCIe\_KEYB\_CLK+/ PCIe\_KEYB\_CLK-: PCI Express Reference Clock for port #0, Differential Pair

PCIE\_RST0#: Reset Signal that is sent from the SoC to all PCI-e devices available on the board. It is a  $+3.3V_RUN$  active-low signal with  $100k\Omega$  pull-down.

CLK\_REQ0#: PCI Express Clock Request Input, active low signal. This signal shall be driven low by any module inserted in the connectivity slot, in order to ensure that the SoC makes available the reference clock. Electrical level  $+3.3V_RUN$  with a  $47K\Omega$  pull-up resistor.

PCIe\_WAKE0#: Board's Wake Input, 3.3V\_RUN active low signal with  $47k\Omega$  pull-up resistor. It must be externally driven by the Connectivity module plugged in the slot when it requires waking up the system.

Here following the signals related to the USB interface:

USB\_P1+/USB\_P1-: USB Port #1 differential pair; it is managed by Microchip USB4604 Hub controller's Downstream Port #1.

M2\_KEYB\_PWROFF#: Power Off signal for plugged modules, usually used in battery-powered systems. Fixed  $2k2\Omega$  pull-up @  $1.8V_RUN$ .

M2\_KEYB\_W\_DIS1#: M.2 module disable signal #1, active low output.

M2\_KEYB\_W\_DIS1#: M.2 module disable signal #2, active low output.

UIM\_RESET: Reset signal line, sent from M.2 WWAN card to the UIM module.

UIM\_DATA: Bidirectional Data line between M.2 WWAN card and UIM module.

UIM\_CLK: Clock line, output from M.2 WWAN card to the UIM module.

UIM\_PWR: Power line for UIM module.

SIM\_DETECT: Sim Detect output, sent to the WWAN module to signal insertion or removal of the SIM in the slot. This pin can also be forced to be low through the jumper JP1

CONF0, CONF1, CONF2, CONF3: Configuration inputs, +3.3V\_RUN signals with 10kΩ pull-up. This signal is necessary to switch between the S-ATA and the PCI-e signals on the pins 29/31/35/37/41/43/47/49 of connector CN37. When CONFIG\_1 signal is high, then PCI-e x 2 interface is available on connector CN37. When the signal is driven low, then SATA interface will be available. The selection is automatic, according to M.2 specifications for Socket2 Add-In Card configuration Table.

## 3.3.10 microSIM Card Slot

| microSIM Card Slot – CN34 |          |     |          |  |

|---------------------------|----------|-----|----------|--|

| Pin                       | Signal   | Pin | Signal   |  |

| 1                         | UIM_PWR  | 5   | GND      |  |

| 2                         | UIM_RST# | 6   |          |  |

| 3                         | UIM_CLK  | 7   | UIM_DATA |  |

| 4                         |          | 8   |          |  |

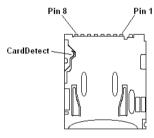

Interfaced to the M.2 slot CN37, there is a microSIM Card Slot, to be used in conjunction with M.2 Socket 2 Key B modems. Here it is possible to insert the microSIM card provided by any telecommunication operator for the connection to their network.

The socket is type MOLEX. p/n 78800-0001or equivalent, with the pinout shown in the table on the left. Signal are described in the above paragraph.

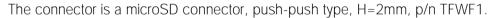

## 3.3.11 microSD Slot

| μSD Card Slot – U43 |           |  |  |

|---------------------|-----------|--|--|

| Pin                 | Signal    |  |  |

| 1                   | SDIO_DAT2 |  |  |

| 2                   | SDIO_DAT3 |  |  |

| 3                   | SDIO_CMD  |  |  |

| 4                   | +3.3V_RUN |  |  |

| 5                   | SDIO_CLK  |  |  |

| 6                   | GND       |  |  |

| 7                   | SDIO_DATO |  |  |

| 8                   | SDIO_DAT1 |  |  |

The i.MX8 Family of SoCs embeds three Ultra Secured Digital Host controller (uSDHC), able to support SD / SDIO / MMC Cards.

One of them is used for the implementation of the optional onboard eMMC drive, another is used to manage the M.2 Socket 1 Key E Slot (CN36, the other one is used to manage a  $\mu$ SD Card Slot for the use of standard microSD cards, which can be used as Mass Storage and/or Boot Devices.

SDIO\_CLK: SD Clock Line (output).

SDIO\_CMD: Command/Response bidirectional line.

SDIO\_DAT[0÷3]: SD Card data bus. SDIO\_DAT0 signal is used for all communication modes. SDIO\_DAT[1÷3] signals are required for 4-bit communication mode.

#### 3.3.12 CAN Connectors

On SBC-C43 board there can be three optional CAN Connectors managed using as many TJA1051 CAN trasnceivers.

CAN Bus Connectors are 6-pin single line SMT connector, type MOLEX 53398-0461 or equivalent, with pinout shown in the tables below. Mating connector: MOLEX 51021-0600 receptacle with MOLEX 50079-8000 female crimp terminals.

On these connectors, the pins CANx\_L\_TERM and CANx\_TERM can be used to insert the 1200hm termination at the end of CAN line. When the termination is needed, then these pins must be connected together.

CANx\_H: High-Level CAN bus line.

CANx\_L: Low-Level CAN bus line.

| CAN BUS #0 - CN46 |             |  |  |

|-------------------|-------------|--|--|

| Pin               | Signal      |  |  |

| 1                 | 12V_ALW     |  |  |

| 2                 | CANO_H      |  |  |

| 3                 | GND         |  |  |

| 4                 | CANO_L      |  |  |

| 5                 | CANO_L_TERM |  |  |

| 6                 | CANO_TERM   |  |  |

| CAN BUS #1 – CN47 |             |  |  |

|-------------------|-------------|--|--|

| Pin               | Signal      |  |  |

| 1                 | 12V_ALW     |  |  |

| 2                 | CAN1_H      |  |  |

| 3                 | GND         |  |  |

| 4                 | CAN1_L      |  |  |

| 5                 | CAN1_L_TERM |  |  |

| 6                 | CAN1_TERM   |  |  |

| CAN BUS #2 – CN48 |  |  |  |

|-------------------|--|--|--|

| Signal            |  |  |  |

| 12V_ALW           |  |  |  |

| CAN2_H            |  |  |  |

| GND               |  |  |  |

| CAN2_L            |  |  |  |

| CAN2_L_TERM       |  |  |  |

| CAN2_TERM         |  |  |  |

|                   |  |  |  |

## 3.3.13 Expansion connectors

SBC-C43 board offers multiple interfaces, like RS-232, RS-485, SPI, I2C and so on, which are carried to three expansion connectors.

| Expansion Connector #1- CN49 |                   |  |

|------------------------------|-------------------|--|

| Pin                          | Signal            |  |

| 1                            | +3.3V_RUN         |  |

| 2                            | GND               |  |

| 3                            | TTL_GPIO_UART2_TX |  |

| 4                            | TTL_GPIO_UART2_RX |  |

| 5                            | RS232_UART2_TX    |  |

| 6                            | RS232_UART3_RX    |  |