# SBC

## User Manual

## SBC-B68-eNUC

SBC with the Intel® Atom™ X Series, Intel® Celeron® J/N Series and Intel® Pentium® N Series (formerly code name Apollo Lake) SoCs in the embedded NUC™ form factor

### REVISION HISTORY

| Revision | Date             | Note                                                                                                                                                                          | Ref |

|----------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.0      | 27 April 2018    | First Official Release.                                                                                                                                                       | SB  |

| 1.1      | 26 February 2018 | Technical Features updated. Aligned to PCB rev. D Breaker references removed in par. 3.3.4 and 3.3.14 BIOS Section updated eDP-to-LVDS accessory section updated (par. 5.2.3) | SB  |

| 1.2      | 21 May 2019      | CN2 P/N corrected CN19 Specification updated and pinout corrected CABKITB68 composition corrected                                                                             | SB  |

| 1.3      | 21 April 2020    | Amplified audio specifications corrected (par. 3.3.5)<br>CN9 pinout corrected (par. 3.3.9)<br>eDP-to-LVDS accessory section updated (par. 5.2.3)                              | SB  |

|          |                  |                                                                                                                                                                               |     |

All rights reserved. All information contained in this manual is proprietary and confidential material of SECO S.p.A.

Unauthorized use, duplication, modification or disclosure of the information to a third-party by any means without prior consent of SECO S.p.A. is prohibited.

Every effort has been made to ensure the accuracy of this manual. However, SECO S.p.A. accepts no responsibility for any inaccuracies, errors or omissions herein. SECO S.p.A. reserves the right to change precise specifications witho Tut prior notice to supply the best product possible.

For further information on this module or other SECO products, but also to get the required assistance for any and possible issues, please contact us using the dedicated web form available at http://www.seco.com (registration required).

Our team is ready to assist.

## INDEX

| Chapter 1.     | INTRODUCTION                          | 6    |

|----------------|---------------------------------------|------|

| 1.1 Wa         | arranty                               | 7    |

| 1.2 Info       | ormation and assistance               | 8    |

| 1.3 RM         | 1A number request                     | 8    |

| 1.4 Sat        | fety                                  | 9    |

| 1.5 Ele        | ctrostatic discharges                 | 9    |

| 1.6 Ro         | HS compliance                         | 9    |

| 1.7 Ter        | minology and definitions              | .10  |

| 1.8 Ref        | ference specifications                | .12  |

| Chapter 2.     | OVERVIEW                              | .13  |

| 2.1 Intr       | oduction                              | 14   |

| 2.2 Ted        | chnical specifications                | 15   |

| 2.3 Ele        | ctrical specifications                | .16  |

| 2.3.1          | RTC Battery                           | 16   |

| 2.3.2          | Power consumption                     |      |

| 2.3.3          | Power rails naming convention         |      |

|                | echanical specifications              |      |

| 2.5 Blo        | ock diagram                           |      |

| Chapter 3.     | CONNECTORS                            | .21  |

| 3.1 Intr       | oduction                              | . 22 |

| 3.2 Co         | nnectors overview                     | .23  |

| 3.3 Co         | nnectors description                  | . 24 |

| 3.3.1          | Ethernet connectors                   |      |

| 3.3.2          | USB ports                             |      |

| 3.3.3          | miniDP++ Connectors                   |      |

| 3.3.4          | eDP Connector                         |      |

| 3.3.5          | Audio interfaces.                     |      |

| 3.3.6<br>3.3.7 | Buttons / LED header                  |      |

| 3.3.8          | µSD slot                              |      |

| 3.3.9          | S-ATA connectors                      |      |

| 3.3.10         | M.2 SSD/WWAN Slot: Socket 2 Key B     |      |

| 3.3.11         | M.2 Connectivity Slot: Key E Socket 1 |      |

|                |                                       |      |

| 3.3.12     | FAN connectors                             | 36 |

|------------|--------------------------------------------|----|

| 3.3.13     | microSIM Card Slot                         | 37 |

| 3.3.14     | Feature connector.                         | 37 |

| 3.3.15     | Optional IR Receiver                       | 38 |

| Chapter 4. | BIOS SETUP                                 | 39 |

| 4.1 Apti   | o setup Utility                            | 40 |

| 4.2 Maii   | n setup menu                               | 41 |

| 4.2.1      | System Time / System Date                  |    |

| 4.3 Adv    | anced menu                                 |    |

| 4.3.1      | Trusted computing submenu                  | 43 |

| 4.3.2      | ACPI Settings                              | 43 |

| 4.3.3      | S5 RTC Wake Settings submenu               | 44 |

| 4.3.4      | Serial Port Console Redirection submenu    | 44 |

| 4.3.5      | CPU Configuration submenu                  | 46 |

| 4.3.6      | AMI graphic Output Protocol Policy submenu | 47 |

| 4.3.7      | PCI Subsystem settings submenu             |    |

| 4.3.8      | Network Stack configuration submenu        |    |

| 4.3.9      | CSM configuration submenu                  |    |

| 4.3.10     | NVMe configuration submenu                 |    |

| 4.3.11     | SDIO configuration submenu                 |    |

| 4.3.12     | USB configuration submenu.                 |    |

| 4.3.13     | Platform Trust technology submenu          |    |

| 4.3.14     | Main Thermal Configuration submenu.        |    |

| 4.3.15     | HSUART Transceiver. Configuration submenu  |    |

| 4.3.16     | LVDS configuration submenu                 |    |

| 4.3.17     | SMBios Information                         |    |

| 4.3.18     | ACPI Devices configuration submenu         |    |

| 4.3.19     | Embedded Controller submenu                |    |

| •          | oset menu                                  |    |

| 4.4.1      | South Bridge submenu                       |    |

| 4.4.2      | Uncore Configuration submenu               |    |

| 4.4.3      | South Cluster Configuration submenu        |    |

|            | urity menu                                 |    |

| 4.5.1      | Secure Boot submenu                        |    |

|            | t menut                                    |    |

|            | e & Exit menu                              |    |

| Chapter 5. | APPENDICES                                 | 66 |

| 5.1 | _     | Thermal Design                       | . 67 |

|-----|-------|--------------------------------------|------|

| 5.2 | /     | Accessories                          | .68  |

|     | 5.2.1 | Accessories kit CABKITB68            | . 68 |

| !   | 5.2.2 | USB-to-Serial port converter modules | . 69 |

|     | 5.2.3 | eDP-to-LVDS converter                | . 70 |

## Chapter 1. INTRODUCTION

- Warranty

- Information and assistance

- RMA number request

- Safety

- Electrostatic discharges

- RoHS compliance

- Terminology and definitions

- Reference specifications

## 1.1 Warranty

This product is subject to the Italian Law Decree 24/2002, acting European Directive 1999/44/CE on matters of sale and warranties to consumers.

The warranty on this product lasts for 1 year.

Under the warranty period, the Supplier guarantees the buyer assistance and service for repairing, replacing or credit of the item, at the Supplier's own discretion.

Shipping costs that apply to non-conforming items or items that need replacement are to be paid by the customer.

Items cannot be returned unless previously authorized by the supplier.

The authorization is released after completing the specific form available on the web-site <a href="http://www.seco.com/en/prerma">http://www.seco.com/en/prerma</a> (RMA Online). The RMA authorization number must be put both on the packaging and on the documents shipped with the items, which must include all the accessories in their original packaging, with no signs of damage to, or tampering with, any returned item.

The error analysis form identifying the fault type must be completed by the customer and has must accompany the returned item.

If any of the above mentioned requirements for the RMA is not satisfied, the item will be shipped back and the customer will have to pay any and all shipping costs.

Following a technical analysis, the supplier will verify if all the requirements, for which a warranty service applies, are met. If the warranty cannot be applied, the Supplier will calculate the minimum cost of this initial analysis on the item and the repair costs. Costs for replaced components will be calculated separately.

Warning!

All changes or modifications to the equipment not explicitly approved by SECO S.p.A. could impair the equipment's functionalities and could void the warranty

### 1.2 Information and assistance

What do I have to do if the product is faulty?

SECO S.p.A. offers the following services:

- SECO website: visit <a href="http://www.seco.com">http://www.seco.com</a> to receive the latest information on the product. In most cases it is possible to find useful information to solve the problem.

- SECO Sales Representative: the Sales Rep can help to determine the exact cause of the problem and search for the best solution.

- SECO Help-Desk: contact SECO Technical Assistance. A technician is at disposal to understand the exact origin of the problem and suggest the correct solution.

E-mail: technical.service@seco.com

Fax (+39) 0575 340434

- Repair centre: it is possible to send the faulty product to the SECO Repair Centre. In this case, follow this procedure:

- o Returned items must be accompanied by a RMA Number. Items sent without the RMA number will be not accepted.

- o Returned items must be shipped in an appropriate package. SECO is not responsible for damages caused by accidental drop, improper usage, or customer neglect.

Note: Please have the following information before asking for technical assistance:

- Name and serial number of the product;

- Description of Customer's peripheral connections;

- Description of Customer's software (operating system, version, application software, etc.);

- A complete description of the problem;

- The exact words of every kind of error message encountered.

## 1.3 RMA number request

To request a RMA number, please visit SECO's web-site. On the home page, please select "RMA Online" and follow the procedure described.

A RMA Number will be sent within 1 working day (only for on-line RMA requests).

## 1.4 Safety

The SBC-B68-eNUC board uses only extremely-low voltages.

While handling the board, please use extreme caution to avoid any kind of risk or damages to electronic components.

Always switch the power off, and unplug the power supply unit, before handling the board and/or connecting cables or other boards.

Avoid using metallic components - like paper clips, screws and similar - near the board when connected to a power supply, to avoid short circuits due to unwanted contacts with other board components.

If the board has become wet, never connect it to any external power supply unit or battery.

Check carefully that all cables are correctly connected and that they are not damaged.

## 1.5 Electrostatic discharges

The SBC-B68-eNUC board, like any other electronic product, is an electrostatic sensitive device: high voltages caused by static electricity could damage some or all the devices and/or components on-board.

Whenever handling a SBC-B68-eNUC board, ground yourself through an anti-static wrist strap. Placement of the board on an anti-static surface is also highly recommended.

## 1.6 RoHS compliance

The SBC-B68-eNUC board is designed using RoHS compliant components and is manufactured on a lead-free production line. It is therefore fully RoHS compliant.

## 1.7 Terminology and definitions

ACPI Advanced Configuration and Power Interface, an open industrial standard for the board's devices configuration and power management

AHCI Advanced Host Controller Interface, a standard which defines the operation modes of SATA interface

API Application Program Interface, a set of commands and functions that can be used by programmers for writing software for specific Operating

Systems

BIOS Basic Input / Output System, the Firmware Interface that initializes the board before the OS starts loading

CEC Consumer Electronics Control, an HDMI feature which allows controlling more devices connected together by using only one remote control

DDC Display Data Channel, a kind of I2C interface for digital communication between displays and graphics processing units (GPU)

DDR Double Data Rate, a typology of memory devices which transfer data both on the rising and on the falling edge of the clock

DDR3L DDR, 3rd generation, Low voltage

DP++ Multimode Display Port, a video interface which can support both Display Port displays (directly) and HDMI/DVI displays (by using and external

adapter)

eDP embedded Display Port

FFC/FPC Flexible Flat Cable / Flat Panel Cable

GBE Gigabit Ethernet

Gbps Gigabits per second

GND Ground

GPI/O General purpose Input/Output

HD Audio High Definition Audio, most recent standard for hardware codecs developed by Intel® in 2004 for higher audio quality

HDMI High Definition Multimedia Interface, a digital audio and video interface

12C Bus Inter-Integrated Circuit Bus, a simple serial bus consisting only of data and clock line, with multi-master capability

Internet of Things

M.2 recent specifications for internal expansion modules, which defines many pinouts and sizes for different purposes. Can include SATA, PCI Express,

USB, UART, DP interfaces

Mbps Megabits per second

MMC/eMMC MultiMedia Card / embedded MMC, a type of memory card, having the same interface as the SD card. The eMMC is the embedded version of the

MMC. They are devices that incorporate the flash memories on a single BGA chip.

N.A. Not ApplicableN.C. Not Connected

OpenCL Open Computing Language, a software library based on C99 programming language, conceived explicitly to realise parallel computing using

Graphics Processing Units (GPU)

OpenGL Open Graphics Library, an Open Source API dedicated to 2D and 3D graphics

OS Operating System

PCI-e Peripheral Component Interface Express

PSU Power Supply Unit

PWM Pulse Width Modulation

PWR Power

PXE Preboot Execution Environment, a way to perform the boot from the network ignoring local data storage devices and/or the installed OS

SATA Serial Advance Technology Attachment, a differential full duplex serial interface for Hard Disks

SD Secure Digital, a memory card type

SIM Subscriber Identity Module, a card which stores all data of the owner

SM Bus System Management Bus, a subset of the I2C bus dedicated to communication with devices for system management, like a smart battery and

other power supply-related devices

SPI Serial Peripheral Interface, a 4-Wire synchronous full-duplex serial interface which is composed of a master and one or more slaves, individually

enabled through a Chip Select line

TBM To be measured

TDP Thermal Design Power, an indication of the amount of heat generated by the processor that must be used for the design of the thermal solution.

TMDS Transition-Minimized Differential Signaling, a method for transmitting high speed serial data, normally used on DVI and HDMI interfaces

UEFI Unified Extensible Firmware Interface, a specification defining the interface between the OS and the board's firmware. It is meant to replace the

original BIOS interface

UIM User Identity Module, an extension of SIM modules.

USB Universal Serial Bus V\_REF Voltage reference Pin

xHCl eXtensible Host Controller Interface, Host controller for USB 3.0 ports, which can also manage USB 2.0 and USB1.1 ports

## 1.8 Reference specifications

Here below it is a list of applicable industry specifications and reference documents.

| Reference                                                                                                  | Link                                                                                                                       |

|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| ACPI                                                                                                       | http://www.acpi.info                                                                                                       |

| AHCI                                                                                                       | http://www.intel.com/content/www/us/en/io/serial-ata/ahci.html                                                             |

| DDC                                                                                                        | http://www.vesa.org                                                                                                        |

| embedded NUC™                                                                                              | http://www.sget.org/fileadmin/ migrated/content uploads/SGET Specification embedded NUC SFF V100.pdf                       |

| Gigabit Ethernet                                                                                           | http://standards.ieee.org/about/get/802/802.3.html                                                                         |

| HD Audio                                                                                                   | http://www.intel.com/content/dam/www/public/us/en/documents/product-specifications/high-definition-audio-specification.pdf |

| HDMI                                                                                                       | http://www.hdmi.org/index.aspx                                                                                             |

| I2C                                                                                                        | http://www.nxp.com/documents/other/UM10204_v5.pdf                                                                          |

| Intel® Front Panel I/O connectivity DG                                                                     | http://www.formfactors.org/developer/specs/A2928604-005.pdf                                                                |

| M.2                                                                                                        | http://pcisig.com/specifications                                                                                           |

| MMC/eMMC                                                                                                   | http://www.jedec.org/committees/jc-649                                                                                     |

| OpenCL                                                                                                     | http://www.khronos.org/opencl                                                                                              |

| OpenGL                                                                                                     | http://www.opengl.org                                                                                                      |

| PCI Express                                                                                                | http://www.pcisig.com/specifications/pciexpress                                                                            |

| SATA                                                                                                       | https://www.sata-io.org                                                                                                    |

| SD Card Association                                                                                        | https://www.sdcard.org/home                                                                                                |

| SM Bus                                                                                                     | http://www.smbus.org/specs                                                                                                 |

| TMDS                                                                                                       | http://www.siliconimage.com/technologies/tmds                                                                              |

| UEFI                                                                                                       | http://www.uefi.org                                                                                                        |

| USB 2.0 and USB OTG                                                                                        | http://www.usb.org/developers/docs/usb 20 070113.zip                                                                       |

| USB 3.0                                                                                                    | http://www.usb.org/developers/docs/usb_30_spec_070113.zip                                                                  |

| Intel <sup>®</sup> Atom <sup>™</sup> , Pentium <sup>®</sup> and Celeron <sup>®</sup><br>Apollo Lake family | http://ark.intel.com/products/codename/80644/Apollo-Lake#@Embedded                                                         |

# Chapter 2. OVERVIEW

- Introduction

- Technical specifications

- Electrical specifications

- Mechanical specifications

- Block diagram

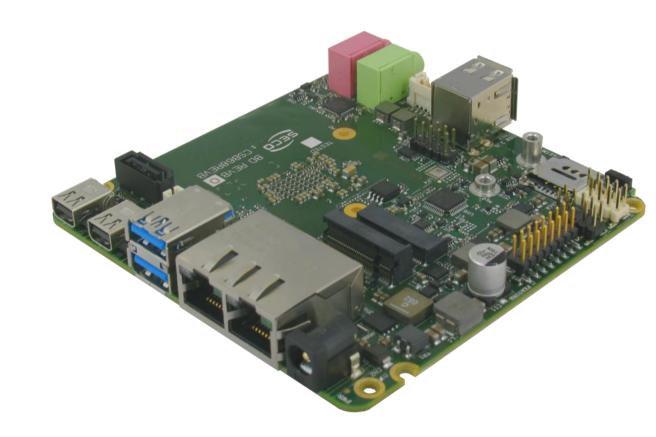

### 2.1 Introduction

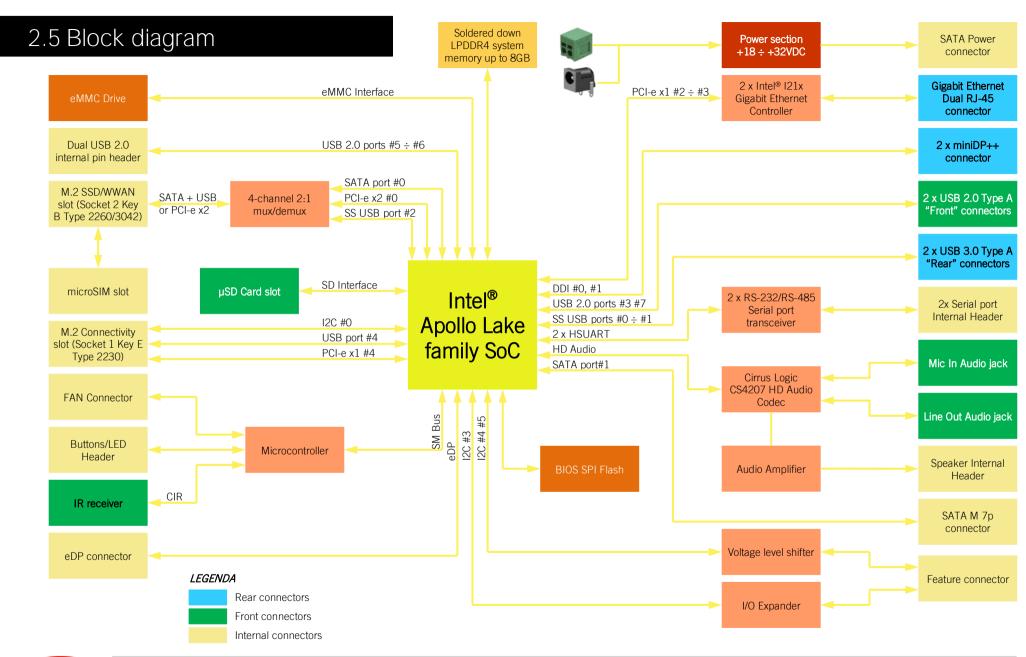

SBC-B68-eNUC is a Single Board Computer in embedded NUC<sup>™</sup> form factor (just 101.6 x 101.6mm) based on the 8<sup>th</sup> generation Intel<sup>®</sup> Atom<sup>™</sup>, Pentium<sup>®</sup> and Celeron<sup>®</sup> family of System-on-Chips (SOCs) formerly coded as Apollo Lake, a series of Dual / Quad SOCs with 64-bit instruction set.

These SoCs embed all the features usually obtained by combination of CPU + platform controller hubs, all in one single IC, which allows, therefore, the system minimisation and performance optimisation, which is essential for boards with sizes so reduced as for embedded  $NUC^{TM}$  SBCs.

The board is also available in EXTREME configuration, with all the components mounted onboard certified for industrial temperature ranges (this configuration is not available with the Celeron® processors).

The embedded memory controller allows the integration of up to 8GB of LPDDR4 Memory directly soldered onboard, speed up to 2400MT/s.

All SOCs embed an Intel® HD Graphics 500 series controller, which offer high graphical performances, with support for Microsoft® DirectX12, OpenGL 4.3, OpenGL 1.2, OpenGLES 3.0 and HW acceleration for video encoding and decoding of HEVC (H.265), H.264, JPEG/MJPEG. It is also possible the HW video decoding only of VP9, MPEG2, VC-1 and WMV9.

This embedded GPU is able to drive three independent displays, by using the miniDP++ and eDP interfaces. Any combinations of these video interfaces are supported.

Further features, managed directly by the Intel® Atom™, Pentium® and Celeron® family of System-on-Chips (SOCs) SoCs and included in SBC-B68-eNUC board, are two SATA Channels (one used for the common SATA / SSD drives, the other used to implement a M.2 Socket 2 Key B SSD/WWAN slot), microSD interface, eight USB ports (two USB 3.0 and two further USB 2.0 on standard Type-A sockets, one USB 2.0 on M.2 Socket 1 Key E Connectivity slot, one USB 3.0 on M.2 Socket 2 Key B SSD/WWAN slot and two USB 2.0 on internal pin header), HD Audio, two UARTs (which are made available with software-configurable RS-232 / RS-422 / RS-485 interface) and five PCI Express lanes (two PCI express lanes are used for the implementation of two Gigabit Ethernet interfaces, a PCI-e x1 lane is carried out on M.2 Socket 1 Key E Connectivity slot, a PCI-e x2 port is shared on M.2 Socket 2 Key B SSD/WWAN slot)

This board is suitable both for IoT applications, due to its rich connectivity, and for industrial applications, since it can accept supply voltages in the range  $+18V_{DC} \div 32V_{DC}$  (recommended voltage range).

The board offers the possibility of expansion by using M.2 modules (both for mass storage and connectivity expansion), which is one of the most recent standards for expansion modules. This guarantees to the SBC-B68-eNUC board a wide possibility of expandability even for the future.

Please refer to following chapter for a complete list of all peripherals integrated and characteristics.

## 2.2 Technical specifications

#### SoC

Intel® Atom™ x7-E3950, Quad Core @1.6GHz (Burst 2.0GHz), 2MB L2 Cache, 12W TDP Intel® Atom™ x5-E3940, Quad Core @1.6GHz (Burst 1.8GHz), 2MB L2 Cache, 9.5W TDP Intel® Atom™ x5-E3930, Dual Core @1.3GHz (Burst 1.8GHz), 2MB L2Cache, 6.5W TDP Intel® Pentium® N4200, Quad Core @1.1GHz (Burst 2.5GHz), 2MB L2 Cache, 6W TDP Intel® Celeron® N3350, Dual Core @1.1GHz (Burst 2.4GHz), 2MB L2Cache, 6W TDP Intel® Celeron® J3455, Quad Core @1.5GHz (Burst 2.3GHz), 2MB L2Cache, 10W TDP Intel® Celeron® J3355, Dual Core @2.0GHz (Burst 2.5 GHz), 2MB L2Cache, 10W TDP

#### Memory

Quad Channel Soldered Down LPDDR4 memory, up to 8GB

#### Graphics

Integrated Intel® HD Graphics 500 series controller with up to 18 Execution Units Three independent display support

HW decoding of HEVC(H.265), H.264, MVC , VP8, VP9, MPEG2, VC-1, WMV9, JPEG/MJPEG formats

HW encoding of HEVC(H.265), H.264, MVC, VP8, VP9 and JPEG/MPEG formats

#### Video Interfaces

Two DP++ 1.2 interfaces on miniDP connectors (supports HDMI displays through external adapter)

embedded Display Port (eDP) internal connector

LVDS through optional external adapter

#### Video Resolution

HDMI, eDP: Up to 3840x2160 (4K) DP++: Up to 4096x2160 LVDS: Up to 1920 x 1200

#### Mass Storage

Optional eMMC drive onboard SATA 7p M connector M.2 SATA SSD slot (Socket 2 Key B Type 3042/2260 \*) microSD Card slot

#### Networking

2x Gbit LAN / Intel Gigabit Ethernet i21x family controller M.2 WWAN Slot for Modems (Socket 2 Key B Type 3042/2260 \*) M.2 WLAN Connectivity Slot for WiFi/BT (Socket 1 Key E type 2230)

#### USB

2 x USB 3.0 Host ports on Type-A sockets 2 x USB 2.0 Host ports on Type-A sockets 2 x USB 2.0 Host port on internal pin header 1 x USB 3.0 Host port on SSD/WWAN M.2 slot (\*) 1 x USB 2.0 Host port on WLAN M.2 Slot

#### **PCI-Express**

1 x PCI-e x2 port on M.2 SSD/WWAN Slot 1 x PCI-e x1 port on M.2 WLAN Slot

#### Audio

HD Audio Codec Cirrus Logic CS4207 Mic In and Line out Audio jacks Amplified Speaker Output on internal pin header

#### Serial Ports

2 x RS-232 / RS-422 / RS-485 Serial ports on internal pin Header (software configurable)

#### Other Interfaces

2 x I2C + 8 x GPI/Os on Feature connector Button/LED Front Panel Header CIR (Consumer InfraRed) Sensor microSIM slot for M.2 WWAN Modem

Power supply:  $+18V_{DC} \div + 32V_{DC}$  recommended

+15V<sub>DC</sub> ÷ +36V<sub>DC</sub> absolute

RTC Battery

Operating temperature:  $0^{\circ}C \div +60^{\circ}C^{**}$  (Commercial temperature)

-40°C ÷ +85°C (Industrial version)

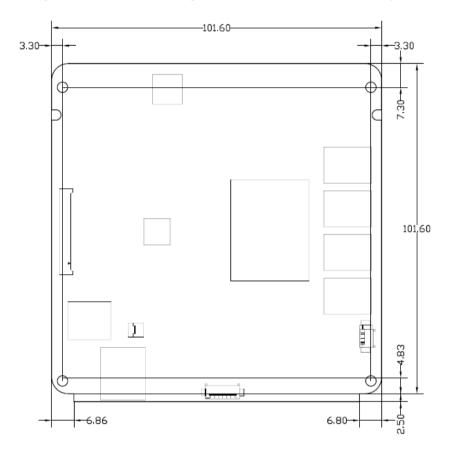

Dimensions: 101.6 x 101.6 mm (4" x 4").

Supported Operating Systems:

Microsoft® Windows 10 Enterprise (64 bit)

Microsoft® Windows 10 IoT Core

Wind River Linux (64 bit)

Yocto (64 bit)

\*\* \*Measured at any point of SECO standard heatspreader for this product, during any and all times (including start-up). Actual temperature will widely depend on application, enclosure and/or environment. Upon customer to consider application-specific cooling solutions for the final system to keep the heatspreader temperature in the range indicated. Please also check paragraph 5.1

<sup>\*</sup> SATA SSD + USB 3.0 and WWAN functionalities share the same slot and are therefore mutually exclusive

## 2.3 Electrical specifications

The SBC-B68-eNUC board can be supplied with any voltage in the range  $+18V_{DC} \div +32V_{DC}$  range (recommended voltage range)

This voltage can be supplied through a standard 6.3mm (internal pin, diameter 2.0 mm) Power Jack (CN1). Internal pin is V<sub>IN</sub> power line.

| Pow | Power IN PCB terminal block - CN2 |  |  |  |  |

|-----|-----------------------------------|--|--|--|--|

| Pin | Signal                            |  |  |  |  |

| 1   | $V_{1N}$                          |  |  |  |  |

| 2   | GND                               |  |  |  |  |

As an alternative, the board can be equipped with a 2-position Terminal Block with front spring-cage connection type PHOENIX CONTACT p/n 1990973 or equivalent, which can be used for the connection of an external PSU.

#### 2.3.1 RTC Battery

For the occurrences when the module is not powered with an external power supply, on board there is a cabled coin Lithium Battery to supply, with a 3V voltage, the Real Time Clock embedded inside the Intel® SoC.

Battery used is a cabled CR2032-LD Lithium coin-cell battery, with a nominal capacity of 220mAh.

| Bat | Battery connector - CN3 |  |  |  |  |  |  |

|-----|-------------------------|--|--|--|--|--|--|

| Pin | Signal                  |  |  |  |  |  |  |

| 1   | $V_{RTC}$               |  |  |  |  |  |  |

| 2   | GND                     |  |  |  |  |  |  |

The battery is not rechargeable, and can be connected to the board using dedicated connector CN5 which is a 2-pin p1.27 mm type MOLEX p/n 53261-0271 or equivalent, with pinout shown in the table on the left.

In case of exhaustion, the battery should only be replaced with devices of the same type. Always check the orientation before inserting and make sure that they are aligned correctly and are not damaged or leaking.

Never allow the batteries to become short-circuited during handling.

Lack CAUTION: handling batteries incorrectly or replacing with not-approved devices may present a risk of fire or explosion.

Batteries supplied with SBC-B68-eNUC are compliant to requirements of European Directive 2006/66/EC regarding batteries and accumulators. When putting out of order SBC-B68-eNUC, remove the batteries from the board in order to collect and dispose them according to the requirement of the same European Directive above mentioned. Even when replacing the batteries, the disposal has to be made according to these requirements.

#### 2.3.2 Power consumption

Using the following setup, and using all possible SoCs offered for SBC-B68-eNUC board, the current consumption (RMS) has been measured on the  $V_{IN}$  Voltage line when the board is supplied with a  $+19V_{DC}$  voltage through DC power jack CN1. The power consumption has been measured using a Keysight DC Power Analyzer

- O.S. Windows 10 Enterprise 2016 LTSB

- 8GB Soldered Down LPDDR4 memory

- 32GB eMMC onboard

- USB mouse and keyboard connected

- LG 27UD88 4K Ultra-HD monitor connected to module's miniDP through adapter

- Intel Dual Band Wireless-AC 3168 WiFi + BT card connected to M.2 Key-E slot

- Kingston SUV400S37 120GB SSD connected to module

- Bios Release 1.04 RC01

| Status                                      | SoC / Configuration       |          |          |       |       |  |

|---------------------------------------------|---------------------------|----------|----------|-------|-------|--|

| Status                                      | x7-E3950                  | x5-E3940 | x3-E3930 | N4200 | N3350 |  |

| Idle, power saving configuration            | 193mA Avg.<br>28mA Peak   | TBM      | TBM      | TBM   | TBM   |  |

| OS Boot, power saving configuration         | 320mA Avg.<br>933mA Peak  | TBM      | ТВМ      | TBM   | TBM   |  |

| Intel TAT tool running, maximum performance | 991mA Avg.<br>1347mA Peak | TBM      | ТВМ      | TBM   | TBM   |  |

| Suspend state (S3)                          | 48.7mA                    | TBM      | TBM      | TBM   | TBM   |  |

| Soft-Off State (S4, no deepsleep)           | 43.4mA                    | TBM      | TBM      | TBM   | TBM   |  |

| Soft-Off State (S4, with deepsleep)         | 22.2mA                    | TBM      | TBM      | TBM   | TBM   |  |

Please consider that the power consumption depends strongly on the utilization scenario.

Please also consider that the SBC-B68-eNUC board can accept a wide voltage range; the efficiency of the DC/DC converters, necessary to generate all the voltages used by the module itself and by the peripherals connected, varies with the rise of the input voltage.

For all these reasons, it is recommended to use PSU with a minimum voltage of 40W for basic functionalities

#### 2.3.3 Power rails naming convention

In all the tables contained in this manual, Power rails are named with the following meaning:

\_S: Switched voltages, i.e. power rails that are active only when the board is in ACPI's S0 (Working) state. Examples: +3.3V\_S, +5V\_S.

\_A: Always-on voltages, i.e. power rails that are active both in ACPI's S0 (Working), S3 (Standby) and S5 (Soft Off) state. Examples: +5V\_A, +3.3V\_A.

Other suffixes are used for application specific power rails, which are derived from same voltage value of voltage switched rails, if it is not differently stated (for example,  $+5V_{HDMI}$  is derived from  $+5V_{LDMI}$ , and so on).

## 2.4 Mechanical specifications

According to embedded NUC<sup>™</sup> form factor, board dimensions are 101.6 x 101.6 mm (4" x 4").

The printed circuit of the board is made of twelve layers, some of them are ground planes, for disturbance rejection.

# Chapter 3. CONNECTORS

- Introduction

- Connectors overview

- Connectors description

## 3.1 Introduction

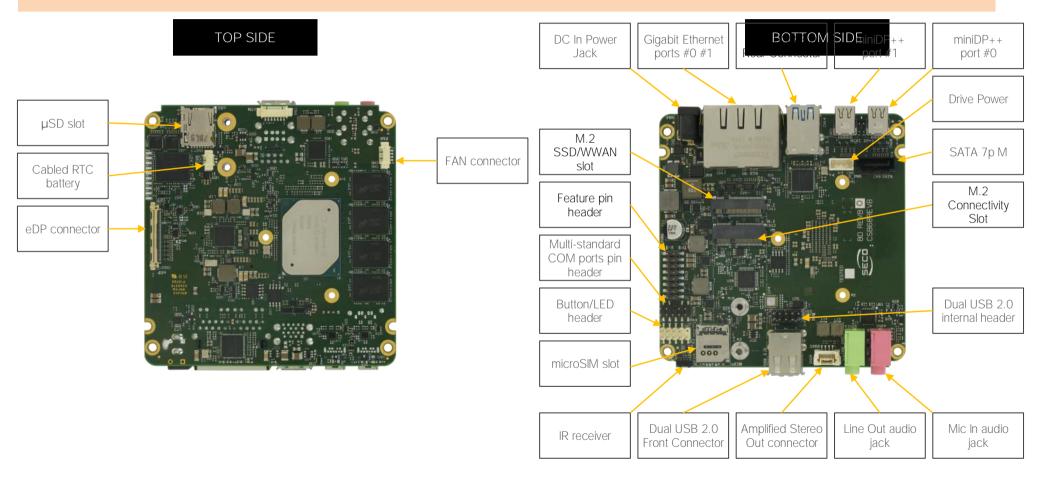

On SBC-B68-eNUC board, there are several connectors located on the upper plane. Standard connectors are placed on the same side of PCB, so that it is possible to place them on a panel of an eventual enclosure.

Please be aware that, depending on the configuration purchased, the appearance of the board could be slightly different from the following pictures.

## 3.2 Connectors overview

| Name | Description                                       | Name | Description                              |

|------|---------------------------------------------------|------|------------------------------------------|

| CN1  | DC IN Power Jack                                  | CN14 | Dual USB 3.0 Rear Connector              |

| CN2  | DC IN PCB terminal block                          | CN15 | Dual USB 2.0 Internal header             |

| CN3  | Cabled RTC Battery                                | CN16 | Multi-standard COM ports internal header |

| CN4  | MFG Connector                                     | CN17 | Dual Gigabit Ethernet connector          |

| CN5  | Optional FAN Header 3p                            | CN19 | Feature connector                        |

| CN6  | FAN Header 4p                                     | CN20 | miniDP++ #0 connector                    |

| CN7  | Button/LED Internal Header                        | CN21 | miniDP++ #1 connector                    |

| CN8  | SATA Port #1 M 7p connector                       | CN22 | eDP internal connector                   |

| CN9  | HDD Power connector                               | CN24 | Mic Audio Jack                           |

| CN10 | microSIM Slot                                     | CN25 | LineOut Audio Jack                       |

| CN11 | M.2 SSD/WWAN Slot (Socket 2 Key B Type 2260/3042) | CN26 | Amplified Stereo Out connector           |

| CN12 | M.2 Connectivity Slot (Socket 1 Key E Type 2230)  | CN27 | μSD Card Slot                            |

| CN13 | Dual USB 2.0 Front Connector                      | U17  | IR Receiver                              |

## 3.3 Connectors description

#### 3.3.1 Ethernet connectors

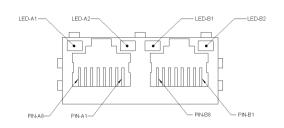

|     | Dual Gigabit Ethernet Ports #0 / #1 - CN17 |            |            |  |  |  |

|-----|--------------------------------------------|------------|------------|--|--|--|

| Pin | Signal                                     | Pin        | Signal     |  |  |  |

| A1  | GBE0_MDI0+                                 | <b>A</b> 5 | GBE0_MDI2- |  |  |  |

| A2  | GBE0_MDI0-                                 | A6         | GBE0_MDI1- |  |  |  |

| А3  | GBE0_MDI1+                                 | A7         | GBE0_MDI3+ |  |  |  |

| A4  | GBE0_MDI2+                                 | A8         | GBE0_MDI3- |  |  |  |

| B1  | GBE1_MDI0+                                 | B5         | GBE1_MDI2- |  |  |  |

| B2  | GBE1_MDI0-                                 | В6         | GBE1_MDI1- |  |  |  |

| В3  | GBE1_MDI1+                                 | В7         | GBE1_MDI3+ |  |  |  |

| B4  | GBE1_MDI2+                                 | В8         | GBE1_MDI3- |  |  |  |

On board, there are two Gigabit Ethernet connections, for the use of two different LANs. Both connections use a dedicated Intel I21x family controller.

Both connections are available on a double port RJ-45 socket type TRXCOM p/n TRJG27420AINL or equivalent, with 2kV decoupling capacitors.

On the connectors there are also two LEDs for each port. Left LED is bicolor (Green /Yellow) and shows 10/100 or 1000 connection: green means 100Mbps connection, yellow means 1000Mpbs connection, when the LED is Off then 10Mpbs or no connection is available. The right LED is Green and shows ACTIVITY presence.

These two interfaces are compatible both with Gigabit Ethernet (1000Mbps) and with Fast Ethernet (10/100Mbps) Networks. They will configure automatically to work with the existing

#### network.

Please be aware that they will work in Gigabit mode only in case that they are connected to Gigabit Ethernet switches/hubs/routers. For the connection, cables category Cat5e or better are required. Cables category Cat6 are recommended for noise reduction and EMC compatibility issues, especially when the length of the cable is significant.

It is also possible to use both Gigabit Ethernet interface simultaneously to perform the link aggregation, useful to increase the throughput of the netwrok connection and to provide also redundancy.

GBEx\_MDI0+/GBEx\_MDI0-: Ethernet Controller #x Media Dependent Interface (MDI) I/O differential pair #0. It is the first differential pair in Gigabit Ethernet mode, and the Transmit differential pair in 10/100 Mbps modes.

GBEx\_MDI1+/GBEx\_MDI1-: Ethernet Controller #x Media Dependent Interface (MDI) I/O differential pair #1. It is the second differential pair in Gigabit Ethernet mode, and the Receive differential pair in 10/100 Mbps modes.

GBEx\_MDI2+/GBEx\_MDI2-: Ethernet Controller #x Media Dependent Interface (MDI) I/O differential pair #2. It is the third differential pair in Gigabit Ethernet mode; it is not used in 10/100Mbps modes.

GBEx\_MDI3+/GBEx\_MDI3-: Ethernet Controller #x Media Dependent Interface (MDI) I/O differential pair #3. It is the fourth differential pair in Gigabit Ethernet mode; it is not used in 10/100Mbps modes.

#### 3.3.2 USB ports

The Intel® Apollo Lake family of SoCs used on SBC-B68-eNUC board can manage up to six USB SuperSpeed (i.e., USB 3.0 compliant) ports and eight High Speed (i.e. USB 2.0 compliant) ports. There are only two dedicated High Speed port, the other four ports are shared with the SuperSpeed ports, i.e. they can be used either by USB 2.0 or USB 3.0.

| U   | USB 3.0 ports Type-A double receptacle - CN14 |     |                     |  |  |  |

|-----|-----------------------------------------------|-----|---------------------|--|--|--|

| Pin | Signal                                        | Pin | Signal              |  |  |  |

| 1   | +5V <sub>USB1</sub>                           | 10  | +5V <sub>USB0</sub> |  |  |  |

| 2   | USB_P1-                                       | 11  | USB_P0-             |  |  |  |

| 3   | USB_P1+                                       | 12  | USB_P0+             |  |  |  |

| 4   | GND                                           | 13  | GND                 |  |  |  |

| 5   | USB_SSRX1-                                    | 14  | USB_SSRX0-          |  |  |  |

| 6   | USB_SSRX1+                                    | 15  | USB_SSRX0+          |  |  |  |

| 7   | GND                                           | 16  | GND                 |  |  |  |

| 8   | USB_SSTX1-                                    | 17  | USB_SSTX0-          |  |  |  |

| 9   | USB_SSTX1+                                    | 18  | USB_SSTX0+          |  |  |  |

The USB 3.0 ports #0 and #1 are available on a double type-A USB 3.0 receptacle, type Würth Elektronik p/n 692141030100 or equivalent.

Since this connector is a standard type receptacle, it can be connected to all types of USB 1.1 / USB 2.0 / USB 3.0 devices using Standard-A USB 3.0 or USB 2.0 plugs.

For USB 3.0 connections it is mandatory the use of SuperSpeed certified cables, whose SuperSpeed differential pairs are individually shielded inside the global cable's external shielding.

|     | USB 2.0 type A receptacle - CN13 |     |                     |  |  |  |

|-----|----------------------------------|-----|---------------------|--|--|--|

| Pin | Signal                           | Pin | Signal              |  |  |  |

| 1   | +5V <sub>USB7</sub>              | 5   | +5V <sub>USB3</sub> |  |  |  |

| 2   | USB_P7-                          | 6   | USB_P3-             |  |  |  |

| 3   | USB_P7+                          | 7   | USB_P3+             |  |  |  |

| 4   | GND                              | 8   | GND                 |  |  |  |

USB 2.0 ports #6 and USB port #3, instead, are carried out on a standard double Type-A receptacle.

Since this connector is a standard type receptacle, it can be connected to all types of USB 1.1 / USB 2.0 devices using Standard-A USB 2.0 cables.

| USB 2.0 ports internal pin header - CN15 |                     |    |                     |  |  |

|------------------------------------------|---------------------|----|---------------------|--|--|

| Pin                                      | n Signal Pin Signal |    |                     |  |  |

| 1                                        | +5V <sub>USB6</sub> | 2  | +5V <sub>USB5</sub> |  |  |

| 3                                        | USB_P6-             | 4  | USB_P5-             |  |  |

| 5                                        | USB_P6+             | 6  | USB_P5+             |  |  |

| 7                                        | GND                 | 8  | GND                 |  |  |

|                                          |                     | 10 |                     |  |  |

There are also two additional USB 2.0 ports, which are hosted on a 9-pin p2.54mm pin header, h= 6mm, type NELTRON p/n 2213S-10G-E9 or equivalent, with the pinout shown in the tables on the left (it is a common pinout for USB headers in PC motherboards).

All USB ports' voltages ( $+5V_{USBx}$ ) are derived from  $+5V_A$  standby voltages. This means that the ports can be powered also when the OS is in Suspend-to-RAM (S3) state in order to support (if enabled) e the "Wake-Up on USB" functionality.

For the connection of standard devices to this pin headers, it is needed an adapter cable. SECO can optionally provide for such an adapter cable, as a part of the accessory kit p/n CABKITB68 (please check chapter 5.2.1 for further details).

#### Signal description:

USB\_P0+/USB\_P0-: USB 2.0 Port #0 differential pair.

USB\_SSRX0+/USB\_SSRX0-: USB Super Speed Port #0 receive differential pair.

USB\_SSTX0+/USB\_SSTX0-: USB Super Speed Port #0 transmit differential pair.

USB\_P1+/USB\_P1-: USB 2.0 Port #1 differential pair.

USB\_SSRX1+/USB\_SSRX1-: USB Super Speed Port #1 receive differential pair.

USB\_SSTX1+/USB\_SSTX1-: USB Super Speed Port #1 transmit differential pair.

USB\_P3+/USB\_P3-: USB 2.0 Port #3 differential pair.

USB\_P5+/USB\_P5-: USB 2.0 Port #5 differential pair.

USB\_P6+/USB\_P6-: USB 2.0 Port #6 differential pair.

USB\_P7+/USB\_P7-: USB 2.0 Port #7 differential pair.

Common mode chokes are placed on all USB differential pairs for EMI compliance.

For ESD protection, on all data and voltage lines are placed clamping diodes for voltage transient suppression.

#### 3.3.3 miniDP++ Connectors

| \UX+ |

|------|

| AUX- |

|      |

|      |

| miniDP++ Port #1 Connector - CN21 |            |     |                         |

|-----------------------------------|------------|-----|-------------------------|

| Pin                               | Signal     | Pin | Signal                  |

| 1                                 | GND        | 2   | DP1_HPD                 |

| 3                                 | DP1_LANEO+ | 4   | CAD                     |

| 5                                 | DP1_LANEO- | 6   |                         |

| 7                                 | GND        | 8   | GND                     |

| 9                                 | DP1_LANE1+ | 10  | DP1_LANE3+              |

| 11                                | DP1_LANE1- | 12  | DP1_LANE3-              |

| 13                                | GND        | 14  | GND                     |

| 15                                | DP1_LANE2+ | 16  | HDMI1_CTRL_CLK/DP1_AUX+ |

| 17                                | DP1_LANE2- | 18  | HDMI1_CTRL_DAT/DP1_AUX- |

| 19                                | GND        | 20  | +3.3V_S                 |

The Intel® Apollo Lake family of SoCs offer two Digital Display Interfaces, configurable to work in HDMI/DVI/DP++ modes.

On the SBC-B68-eNUC board, both the Digital Display Interfaces are used to implement multimode Display Port (DP++)interfaces, i.e. they can be used to support DP displays directly and, through an external adapter, also HDMI or DVI displays.

These two interfaces are available on as many miniDP connectors, type Pulse Electronics p/n E9320-001-01 or equivalent, with the pinout shown in the table on the left.

The configuration of this interface in DP or HDMI/DVI mode is automatic, and it is driven by the CAD signal available on pin 4.

When a DP cable is connected, then the CAD signal is not connected; this interface will recognize it, and on pins 16/18 there will be the Display Port Auxiliary channel signals. Instead, when a DP-to-HDMI adapter is mounted, it will drive opportunely the CAD signal, which will make available HDMI\_CTRL\_CLK and HDMI\_CTRL\_DAT signals on the same pins.

Further signals involved in DP management are the following:

DPx\_LANEO+/DPx\_LANEO-: Display Port #x differential pair #0.

DPx\_LANE1+/DPx\_LANE1-: Display Port #x differential pair #1.

DPx\_LANE2+/DPx\_LANE2-: Display Port #x differential pair #2.

DPx\_LANE3+/DPx\_LANE3-: Display Port #x differential pair #3.

DPx\_HPD: Port #x Hot Plug Detect Input signal.

#### 3.3.4 eDP Connector

| eDP connector - CN22 |                  |     |          |  |

|----------------------|------------------|-----|----------|--|

| Pin                  | Signal           | Pin | Signal   |  |

| 1                    | PTN_PWR          | 21  | SW_VDD   |  |

| 2                    | SW_BACK          | 22  | SW_VDD   |  |

| 3                    | SW_BACK          | 23  | SW_VDD   |  |

| 4                    | SW_BACK          | 24  | GND      |  |

| 5                    | SW_BACK          | 25  | eDP_AUX- |  |

| 6                    | PTN_SMB_CLK      | 26  | eDP_AUX+ |  |

| 7                    | PTN_SMB_DAT      | 27  | GND      |  |

| 8                    | eDP_BLT_CTRL     | 28  | eDP_TXO+ |  |

| 9                    | eDP_BACKLIGHT_EN | 29  | eDP_TX0- |  |

| 10                   | GND              | 30  | GND      |  |

| 11                   | GND              | 31  | eDP_TX1+ |  |

| 12                   | GND              | 32  | eDP_TX1- |  |

| 13                   | GND              | 33  | GND      |  |

| 14                   | eDP_HPD          | 34  | eDP_TX2+ |  |

| 15                   | GND              | 35  | eDP_TX2- |  |

| 16                   | GND              | 36  | GND      |  |

| 17                   | GND              | 37  | eDP_TX3+ |  |

| 18                   | GND              | 38  | eDP_TX3- |  |

| 19                   |                  | 39  | GND      |  |

| 20                   | SW_VDD           | 40  |          |  |

The Intel® Apollo Lake family of SoCs offer a dedicated embedded Display Port interface.

For the connection of this kind of displays, on-board there is a VESA® certified connectors for embedded Display Port interface, type STARCONN p/n 300E40-0110RA-G3 or equivalent (microcoaxial cable connector, 0.5mm pitch, 40 positions).

On this connector, SW\_BACK and SW\_VDD are the voltage rails that can be used to supply the LCD and related Backlight Unit.

The LCD software-driven voltage, i.e. signal SW\_VDD, can be regulated to be connected to +3.3V A or +5V A.

Similarly, the backlight software-driven voltage, i.e. signal SW\_BACK, can also be regulated to be connected to +5V A or +12V A

These are factory configurations, please take care of specifying which is the configuration needed for both SW\_VDD and SW\_BACK voltage rails.

Here following the signals involved in eDP management:

eDP\_TX0+/eDP\_TX0-: embedded DP differential data pair #0.

eDP\_TX1+/eDP\_TX1-: embedded DP differential data pair #1.

eDP\_TX2+/eDP\_TX2-: embedded DP differential data pair #2.

eDP\_TX3+/eDP\_TX3-: embedded DP differential data pair #3.

eDP\_AUX+/eDP\_AUX-: embedded DP auxiliary channel differential data pair.

eDP\_HPD: embedded DP Hot Plug Detect. Active high signal with  $100k\Omega$  pull-down resistor

eDP\_BACKLIGHT\_EN:  $+3.3V_S$  electrical level Output,  $100k\Omega$  pull-down resistor, Backlight Enable signal. It can be used to turn On/Off the backlight's lamps of connected displays.

eDP\_BLT\_CTRL: this signal can be used to adjust the backlight brightness in displays supporting Pulse Width Modulated (PWM) regulations (+3.3V\_S electrical level,  $100k\Omega$  pull-down resistor).

PTN\_PWR: 3.3V\_S derived voltage for external eDP-to-LVDS bridge adapter (please check par. 5.2.3)

PTN\_SMB\_CLK: SM Bus control clock line for external eDP-to-LVDS bridge adapter. Output signal, electrical level PTN\_PWR with a  $2k2\Omega$  pull-up resistor.

PTN\_SMB\_DAT: SM Bus control data line for external eDP-to-LVDS bridge adapter. Bidirectional signal, electrical level PTN\_PWR with a  $2k2\Omega$  pull-up resistor.

#### 3.3.5 Audio interfaces

In the SBC-B68-eNUC board, audio functionalities are provided by a Cirrus Logic CS4207 High Definition Audio Codec.

Two standard stereo audio jacks are available on-board: the light green (lime) audio jack is the Headphone out (not amplified), while Pink Audio jack is the Mic In.

| Amplified Stereo Connector-<br>CN26 |                         |  |  |

|-------------------------------------|-------------------------|--|--|

| Pin                                 | Signal                  |  |  |

| 1                                   | Speaker Right Channel + |  |  |

| 2                                   | Speaker Right Channel - |  |  |

| 3                                   | Speaker Left Channel -  |  |  |

| 4                                   | Speaker Left Channel +  |  |  |

Additionally, it is also possible to connect external stereo speakers by using the dedicated connector CN26, which is a connector type JST p/n BM04B-ZESS-TB.

Mating connector: JST ZER-04V-S with SZE-002T-P0.3female crimp terminals.

Speaker audio output is internally amplified, and is able to support:

- 2x 8W outputs on  $8\Omega$  speakers;

- 2x 13W outputs on  $4\Omega$  speakers.

- ! Please take care of selecting speakers able to sustain the max power supplied by the audio amplifier

#### 3.3.6 Buttons / LFD header

|     | Buttons / LED Header - CN7 |     |                |  |  |

|-----|----------------------------|-----|----------------|--|--|

| Pin | Signal                     | Pin | Signal         |  |  |

| 1   | HD_LED_P                   | 2   | FP PWR_P/SLP_N |  |  |

| 3   | HD_LED_N                   | 4   | FP PWR_N/SLP_P |  |  |

| 5   | RST_SW_N                   | 6   | PWR_SW_P       |  |  |

| 7   | RST_SW_P                   | 8   | PWR_SW_N       |  |  |

| 9   |                            |     |                |  |  |

To allow the integration of a SBC-B68-eNUC based system inside a box PC-like, there is a connector on the board that allows to remote signals for the Power Button (to be used to put the system in a Soft Off State, or awake from it), for the Reset Button, and the signal for optional LED signaling activity on SATA Channel and Power On states.

The pinout of this connector complies with Intel® Front Panel I/O connectivity Design Guide, Switch/LED Front Panel section, chapter 2.2. It is shown in the table on the left.

Connector CN7 is an internal 9-pin standard male pin header, p 2.54 mm, 5+4 pin, h= 6mm, type NELTRON p/n 2213S-10G-E10 or equivalent.

It is possible to buy SECO's dedicated front panel module, which offers standard connections: two standard audio jacks, two pushbuttons (for reset and power on) and two LEDs, for SATA activity and Power status signaling.

This adapter module is also contained inside the dedicated cable kit (CABKITB68) for SBC-B68-eNUC board. Please also check chapter 5.2.1 for further details.

#### Signals Description

HD\_LED\_P: Hard Disk Activity LED signal's pull-up to  $+5V_S$  voltage (510 $\Omega$  pull-up).

HD\_LED\_N: Hard Disk Activity LED output signal

RST SW N: Reset Button GND

RST SW P: Reset button input signal. This signal has to be connected to an external momentary pushbutton (contacts normally open). When the pushbutton is pressed, the pulse of Reset signal will cause the reset of the board.

PWR\_SW\_P: Power button input signal. This signal has to be connected to an external momentary pushbutton (contacts normally open). Upon the pressure of this pushbutton, the pulse of this signal will let the switched voltage rails turn on or off.

PWR SW N: Power button GND

FP PWR P/SLP N: Power/Sleep messaging LED terminal 1 with 510Ω pull-up resistor to +5V A voltage. Connect it to an extremity of a dual-color power LED for power ON/OF, sleep and message waiting signaling. Please refer to Intel® Front Panel I/O connectivity Design Guide, chapter 2,2,4, for LED functionalities and signal. meaning.

FP PWR N/SLP P: Power/Sleep messaging LED terminal 2 with 510Ω pull-up resistor to +5V A voltage. Connect it to the other extremity of the dual-color power LED above mentioned.

#### 3.3.7 Multi-standard serial ports

|     | Dual RS-232/RS-422/RS-485 pin header- CN16 |                    |                    |  |  |  |

|-----|--------------------------------------------|--------------------|--------------------|--|--|--|

| Pin | Signal RS-232 mode                         | Signal RS-422 mode | Signal RS-485 mode |  |  |  |

| 1   | COM1_RxD                                   | COM1_Rx+           |                    |  |  |  |

| 2   | COM2_RxD                                   | COM2_Rx+           |                    |  |  |  |

| 3   | COM1_TxD                                   | COM1_Tx-           | COM1_Data-         |  |  |  |

| 4   | COM2_TxD                                   | COM2_Tx-           | COM2_Data-         |  |  |  |

| 5   | GND                                        | GND                | GND                |  |  |  |

|     |                                            |                    |                    |  |  |  |

| 7   | COM1_RTS#                                  | COM1_Tx+           | COM1_Data+         |  |  |  |

| 8   | COM2_RTS#                                  | COM2_Tx+           | COM2_Data+         |  |  |  |

| 9   | COM1_CTS#                                  | COM1_Rx-           |                    |  |  |  |

| 10  | COM2_CTS#                                  | COM2_Rx-           |                    |  |  |  |

The Intel® Apollo Lake family of SoCs embed three high speed UART controllers, which support COM ports with flow control (RTS# and CTS# signals).

Two of these ports (HSUART #0 and #2) are carried, on SBC-B68-eNUC board to as many multistandard RS-23/RS-422/RS-485 transceivers, allowing the implementation of two multistandard serial ports (from now on respectively named COM1 and COM2).

These ports are available on dedicated connector CN16, which is an internal 9-pin standard male pin header, p 2.54 mm, 5+4 pin, h = 6mm, type NELTRON p/n 2213S-10G-E06 or equivalent.

Signals Description

COM1\_RxD/COM2\_RxD: COM port #1 / #2 RS-232 Receive data

COM1\_TxD/COM2\_TxD: COM port #1 / #2x RS-232 Transmit data

COM1\_RTS#/COM2\_RTS#: COM port #1 / #2 RS-232 Request to Send handshaking signal.

COM1\_CTS#/COM2\_CTS#: COM port #1 / #2x RS-232 Clear To Send handshaking signal

COM1\_RX+/COM1\_RX-: COM port #1 RS-422 receive differential pair

COM1\_TX+/COM1\_TX-: COM port #1 RS-422 Transmit differential pair

COM2\_RX+/COM2\_RX-: COM port #2 Full Duplex RS-485 (RS-422) Receive differential pair

COM2\_TX+/COM2\_TX-: COM port #2 Full Duplex RS-485 (RS-422) Transmit differential pair

COM1\_Data+/COM1\_Data-: COM Port #1 Half Duplex RS-485 Differential Pair

COM2\_Data+/COM2\_Data-: COM Port #2 Half Duplex RS-485 Differential Pair

The selection of the kind of interface (RS-232, RS-422 or RS-485) can be made via BIOS (please check par.4.3.12).

Please be aware that for proper RS-485 working, the RTS# signals coming out from the Apollo Lake family of SoCs must be used as an handshaking signal, i.e. it is used to control the data flow direction. When RTS# signal is driven low, then the RS-485 port is in receiving mode, when RTS# signal is driven high then the RS-458 port is in transmitting mode.

Please check paragraphs 4.3.12 and 4.4.3.2 for further details on serial ports enabling and console redirection

#### 3.3.8 µSD slot

The SoCs used on SBC-B68-eNUC module offer a SD 3.0 compliant interface, that can be used to implement another mass storages media other than the optional internal eMMC and the two SATA interfaces.

This SD interface is carried to a standard µSD card slot, soldered on top side of the module, push-push type.

#### 3.3.9 S-ATA connectors

| S-ATA Connector - CN8 |           |  |  |

|-----------------------|-----------|--|--|

| Pin                   | Signal    |  |  |

| 1                     | GND       |  |  |

| 2                     | SATA1_Tx+ |  |  |

| 3                     | SATA1_Tx- |  |  |

| 4                     | GND       |  |  |

| 5                     | SATA1_Rx- |  |  |

| 6                     | SATA1_Rx+ |  |  |

| 7                     | GND       |  |  |

The Apollo Lake family of SoCs embeds a SATA Controller, which offers two SATA III, 6.0 Gbps interfaces.

Of these interfaces, one SATA channel is carried out to a standard male S-ATA connector, CN8 (the other SATA channel is available on the M.2 KeyB socket, CN11, please check par. 3.3.10).

Here following the signals related to SATA interface:

SATA1\_TX+/SATA1\_TX-: Serial ATA Channel #1 Transmit differential pair

SATA1\_RX+/SATA1\_RX-: Serial ATA Channel #1 Receive differential pair

10nF AC series decoupling capacitors are placed on each line of SATA differential pairs.

### S-ATA Power Connector - CN9

| Pin | Signal |

|-----|--------|

| 1   |        |

| 2   | GND    |

| 3   | GND    |

| 4   | +5V_S  |

A dedicated power connector, CN9, can be used to give supply to external Hard Disks (or Solid State Disks) connected to the SATA male connector.

The dedicated power connector is a 4-pin male connector, type MOLEX p/n 89400-0420 or equivalent, with pinout shown in the table on the left.

Mating connector: MOLEX 87369-0400 crimp housing with MOLEX 50212 crimp terminals.

An adapter cable for powering SATA disks from this connector is also contained inside the dedicated cable kit (CABKITB68) for SBC-B68-eNUC board. Please also check chapter 5.2.1 for further details.

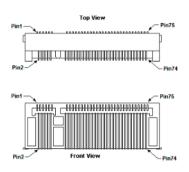

#### 3.3.10 M.2 SSD/WWAN Slot: Socket 2 Key B

| M.2 SSD/WWAN Slot (Socket 2 Key B type 3042/2260- CN11) |                       |     |                      |  |

|---------------------------------------------------------|-----------------------|-----|----------------------|--|

| Pin                                                     | Signal                | Pin | Signal               |  |

| 1                                                       | CONF3                 | 2   | +3.3V_M2             |  |

| 3                                                       | GND                   | 4   | +3.3V_M2             |  |

| 5                                                       | GND                   | 6   | FULL_CARD_POWER_OFF# |  |

| 7                                                       | USB_P2-               | 8   | W_DISABLE1#          |  |

| 9                                                       | USB_P2+               | 10  |                      |  |

| 11                                                      | GND                   |     |                      |  |

|                                                         |                       | 20  |                      |  |

| 21                                                      | CONF0                 | 22  |                      |  |

| 23                                                      | WWAN_WAKE#            | 24  |                      |  |

| 25                                                      |                       | 26  | W_DISABLE2#          |  |

| 27                                                      | GND                   | 28  |                      |  |

| 29                                                      | PCle0_Rx1-/USB_SSRX2- | 30  | UIM_RESET            |  |

| 31                                                      | PCle0_Rx1+/USB_SSRX2+ | 32  | UIM_CLK              |  |

| 33                                                      | GND                   | 34  | UIM_DATA             |  |

| 35                                                      | PCle0_Tx1-/USB_SSTX2- | 36  | UIM_PWR              |  |

| 37                                                      | PCle0_Tx1+/USB_SSTX2+ | 38  |                      |  |

| 39                                                      | GND                   | 40  |                      |  |

| 41                                                      | PCle0_Rx0+/SATA0_RX+  | 42  |                      |  |

| 43                                                      | PCle0_Rx0-/SATA0_RX-  | 44  |                      |  |

| 45                                                      | GND                   | 46  |                      |  |

| 47                                                      | PCle0_Tx0-/SATA0_TX-  | 48  |                      |  |

| 49                                                      | PCle0_Tx0+/SATA0_TX+  | 50  | PLT_RST#             |  |

| 51                                                      | GND                   | 52  | PCIe_REQ0#           |  |

| 53                                                      | PCle0_CLK+            | 54  | PCIe_WAKE0#          |  |

| 55                                                      | PCle0_CLK-            | 56  |                      |  |

| 57                                                      | GND                   | 58  |                      |  |

The mass storage capabilities of the SBC-B68-eNUC are completed by an M.2 SSD Slot, which allow plugging M.2 Socket 2 Key B Solid State Drives.

The same slot can be used alternatively for the connection of Connectivity modules, using PCI-e x2 interface or USB 3.0 interface (USB interface is available simultaneously to SATA interface; both of them are alternative to PCI-e interface).

The connector used for the M.2 SSD slot is CN11, which is a standard 75 pin M.2 Key B connector, type LOTES p/n APCI0087-P001A, H=8.5mm, with the pinout shown in the table on the left.

On the SBC-B68-eNUC board there is also a Threaded Spacer which allows the placement of M.2 Socket 2 Key B SSD modules in 2260 size.

It is possible to place also modules in 2242 / 3042 size, by using a M/F Spacer which allow fixing the M.2 SSD on the spacer already available on the PCB, deemed for the fixing of the M.2 connectivity slot (see next paragraph).

Here following the signals related to the SATA interface:

SATAO\_TX+/SATAO\_TX-: Serial ATA Channel #0 Transmit differential pair

SATAO\_RX+/SATAO\_RX-: Serial ATA Channel #0 Receive differential pair

10nF AC series decoupling capacitors are placed on each line of SATA differential pairs.

Here following the signals related to the PCI-e interface:

PCle0\_Tx0+/PCle0\_Tx0-: PCl Express port #0 lane #0, Transmitting Output Differential pair

PCleO\_RxO+/PCleO\_RxO-: PCl Express port #0 lane #0, Receiving Input Differential pair

PCle0\_Tx1+/PCle0\_Tx1-: PCl Express port #0 lane #1, Transmitting Output Differential pair

PCle0\_Rx1+/PCle0\_Rx1-: PCl Express port #0 lane #1, Receiving Input Differential pair

PCle0\_Clock+ / PCle0\_Clock-: PCl Express Reference Clock for port #0, Differential Pair

PLT\_RST#: Reset Signal that is sent from the SoC to all PCI-e devices available on the board (i.e. the GbE controllers, the PCI-e based modules plugged in the CN11 slot and the

| 59 |       | 60 |          |

|----|-------|----|----------|

| 61 |       | 62 |          |

| 63 |       | 64 |          |

| 65 |       | 66 |          |

| 67 |       | 68 |          |

| 69 | CONF1 | 70 | +3.3V_M2 |

| 71 | GND   | 72 | +3.3V_M2 |

| 73 | GND   | 74 | +3.3V_M2 |

| 75 | CONF2 |    |          |

connectivity modules plugged in CN12 slot). It is a 3.3V active-low signal.

PCIe\_REQ0#: PCI Express Clock Request Input, active low signal. This signal shall be driven low by any module inserted in the connectivity slot, in order to ensure that the SoC makes available the reference clock.

PCIe\_WAKE0#: Board's Wake Input, 3.3V\_A active low signal with  $10k\Omega$  pull-up resistor. It must be externally driven by the Connectivity module plugged in the slot when it requires waking up the system.

Here following the signals related to the USB interface:

USB\_P2+/USB\_P2-: USB 2.0 Port #2 differential pair.

USB\_SSRX2+/USB\_SSRX2-: USB Super Speed Port #2 receive differential pair.

USB\_SSTX2+/USB\_SSTX2-: USB Super Speed Port #2 transmit differential pair.

FULL\_CARD\_POWER\_OFF#: Power Off signal for plugged modules, usually used in battery-powered systems. Fixed 2k2Ω pull-up @ 1.8V\_A.

W\_DISABLE1#: M.2 module disable signal #1, 3.3V\_M2 active low output

W\_DISABLE2#: M.2 module disable signal #2, 3.3V\_M2 active low output

WWAN\_WAKE#: Board's Wake Input, 1.8V\_A active low signal with  $100k\Omega$  pull-up resistor. It must be externally driven by the Connectivity module plugged in the slot when it requires waking up the system (functionality not yet supported by the BIOS).

UIM\_RESET: Reset signal line, sent from M.2 WWAN card to the UIM module.

UIM\_DATA: Bidirectional Data line between M.2 WWAN card and UIM module.

UIM\_CLK: Clock line, output from M.2 WWAN card to the UIM module.

UIM\_PWR: Power line for UIM module.

CONF0, CONF1, CONF2, CONF3: Configuration inputs,  $+3.3V_A$  signals with  $10k\Omega$  pull-up. This signal is necessary to switch between the S-ATA + USB signals and the PCI-e signals on the pins 29/31/35/37/41/43/47/49 of connector CN11. When CONFIG\_1 signal is high, then PCI-e x 2 interface is available on connector CN20. When the signal is driven low, then SATA interface will be available. The selection is automatic, according to M.2 specifications for Socket2 Add-In Card configuration Table.

+3.3V M2: 3.3 voltage for M.2 module, derived from +3.3V A standby voltage.

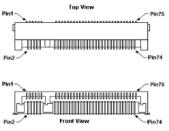

#### 3.3.11 M.2 Connectivity Slot: Key E Socket 1

| M.2 Connectivity Slot: Socket 1 Key E type 2230 - CN12 |             |     |              |  |

|--------------------------------------------------------|-------------|-----|--------------|--|

| Pin                                                    | Signal      | Pin | Signal       |  |

| 1                                                      | GND         | 2   | +3.3V_A      |  |

| 3                                                      | USB_P4+     | 4   | +3.3V_A      |  |

| 5                                                      | USB_P4-     | 6   |              |  |

| 7                                                      | GND         | 8   |              |  |

| 9                                                      |             | 10  |              |  |

| 11                                                     |             | 12  |              |  |

| 13                                                     |             | 14  |              |  |

| 15                                                     |             | 16  |              |  |

| 17                                                     |             | 18  | GND          |  |

| 19                                                     |             | 20  |              |  |

| 21                                                     |             | 22  |              |  |

| 23                                                     |             |     |              |  |

|                                                        |             | 32  |              |  |

| 33                                                     | GND         | 34  |              |  |

| 35                                                     | PCle4_Tx+   | 36  |              |  |

| 37                                                     | PCle4_Tx-   | 38  |              |  |

| 39                                                     | GND         | 40  |              |  |

| 41                                                     | PCle4_Rx+   | 42  |              |  |

| 43                                                     | PCle4_Rx-   | 44  |              |  |

| 45                                                     | GND         | 46  |              |  |

| 47                                                     | PCle4_CLK+  | 48  |              |  |

| 49                                                     | PCle4_CLK-  | 50  | SUS_CLK      |  |

| 51                                                     | GND         | 52  | PLT_RST#     |  |

| 53                                                     | PCle_REQ1#  | 54  | BT_DISABLE#  |  |

| 55                                                     | PCIe_WAKE1# | 56  | WIFI_DISABLE |  |

| 57                                                     | GND         | 58  | M.2_I2C_SDA  |  |

It is possible to increase the connectivity of the SBC-B68-eNUC board by using M.2 Socket 1 Key E connectivity slot.

The connector used for the M.2 Connectivity slot is CN12, which is a standard 75 pin M.2 Key E connector, type LOTES p/n APCI0076-P001A, H=4.2mm, with the pinout shown in the table on the left.

On the SBC-B68-eNUC board there is also a Threaded Spacer which allows the placement of M.2 Socket 1 Key E connectivity modules in 2230 size.

Here following the signals related to this connectivity interface:

USB\_P4+/USB\_P4-: USB 2.0 Port #4 differential pair.

PCle4\_TX+/PCle4\_TX-: PCl Express port #4, Transmitting Output Differential pair

PCle4\_RX+/PCle4\_RX-: PCl Express port #4, Receiving Input Differential pair

PCle4\_Clock+ / PCle4\_Clock-: PCl Express Reference Clock for port #4, Differential Pair

PCIe\_WAKE1#: Board's Wake Input, 3.3V\_A active low signal. It must be externally driven by the Connectivity module inserted in the slot when it requires waking up the system.

PLT\_RST#: Reset Signal that is sent from the SoC to all PCI-e devices available on the board (i.e. the GbE controllers) and on the connectivity module. It is a 3.3V active-low signal.

PCIe\_REQ1#: PCI Express Clock Request Input, active low signal. This signal shall be driven low by any module inserted in the connectivity slot, in order to ensure that the SoC makes available the reference clock.

SUS\_CLK: 32.768kHz Clock provided by the SBC-B68-eNUC board to the module plugged in the slot CN12. +3.3V A electrical level.

BT\_DISABLE#: Bluetooth module disable, active low signal, +3.3V\_A electrical level. This signal can be used to disable Bluetooth functionalities of any connectivity module plugged in CN12 Slot.

WIFI\_DISABLE#; WiFi module disable, active low signal, +3.3V\_A electrical level. This signal can be used to disable WiFi functionalities of any connectivity module plugged in CN16 Slot.

| 59 |     | 60 | M.2_I2C_SCL |

|----|-----|----|-------------|

| 61 |     | 62 | M.2_ALERT#  |

| 63 | GND | 64 |             |

| 65 |     | 66 |             |

| 67 |     | 68 |             |

| 69 | GND | 70 |             |

| 71 |     | 72 | +3.3V_A     |

| 73 |     | 74 | +3.3V_A     |

| 75 | GND |    |             |

M.2\_I2C\_SDA: I2C Bus data line. Bidirectional signal, electrical level  $+3.3V_A$  with a  $2K2\Omega$  pull-up resistor. It is managed by SoC's I2C controller #0.

M.2\_I2C\_SCL: I2C Bus clock line. Bidirectional signal, electrical level +3.3V\_A with a  $2K2\Omega$  pull-up resistor. It is managed by SoC's I2C controller #0.

M.2\_ALERT#: I2C Bus Alert. Input signal, electrical level  $+3.3V_A$  with a  $10K\Omega$  pull-up resistor. It is managed through a SoC's GPIO.

#### 3.3.12 FAN connectors

| FAN Connector - CN6 |              |  |  |

|---------------------|--------------|--|--|

| Pin                 | Signal       |  |  |

| 1                   | GND          |  |  |

| 2                   | FAN_POWER    |  |  |

| 3                   | FAN_TACHO_IN |  |  |

| 4                   | FAN_PWM      |  |  |

Depending on the usage model of SBC-B68-eNUC, for critical applications/environments on SBC-B68-eNUC it is available a 4-pin dedicated connector for an external +5V<sub>DC</sub> FAN.

The default FAN Connector is a 4-pin single line SMT connector, type MOLEX 53261-0471 or equivalent, with pinout shown in the table on the left.

Mating connector: MOLEX 51021-0400 receptacle with MOLEX 50079-8000 female crimp terminals.

## Optional FAN Connector - CN5

|     | CN5          |

|-----|--------------|

| Pin | Signal       |

| 1   | GND          |

| 2   | FAN_POWER    |

| 3   | FAN_TACHO_IN |

Alternatively, as a factory option, the SBC-B68-eNUC module can be equipped with a 3-pin single line SMT connector, type MOLEX 53261-0371 or equivalent, with pinout shown in the table on the left.

Mating connector: MOLEX 51021-0300 receptacle with MOLEX 50079-8000 female crimp terminals.

Please be aware that the use of an external fan depends strongly on customer's application/installation.

Please refer to chapter 5.1 for considerations about thermal dissipation.

FAN\_POWER: +5V\_A derived power rail for FAN.

FAN\_PWM: PWM output from the embedded microcontroller to the FAN (4-pin connector only).

FAN\_TACHO\_IN: tachometric input from the FAN to the embedded microcontroller,  $+3.3V_S$  electrical level signal with  $10k\Omega$  pull-up resistor and Schottky series diode.

#### 3.3.13 microSIM Card Slot

| microSIM Card Slot - CN10 |          |     |          |  |