# Smarc

## User Manual

## HALLEY

SMARC<sup>®</sup> Rel. 2.1.1 compliant module with the Intel<sup>®</sup> Atom<sup>™</sup> x6000E Series and Intel<sup>®</sup> Pentium<sup>®</sup> and Celeron<sup>®</sup> N and J Series processors (formerly Elkhart Lake) for FuSa applications

www.seco.com

### **REVISION HISTORY**

| Revision | Date                           | Note                                                                            | Rif |

|----------|--------------------------------|---------------------------------------------------------------------------------|-----|

| 1.0      | 19 <sup>th</sup> April 2021    | First official release                                                          | AR  |

| 1.1      | 23 <sup>rd</sup> December 2021 | Safety Policy included                                                          | SO  |

| 1.2      | 26 <sup>th</sup> August 2022   | BIOS documentation                                                              | SO  |

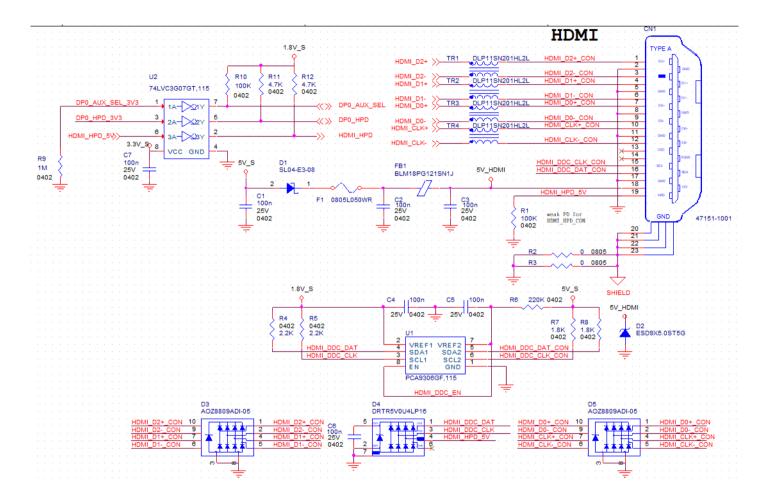

| 1.3      | 13th April 2023                | Included engineering samples policy<br>Included decoupling circuit for HDMI 1.4 | SO  |

#### All rights reserved. All information contained in this manual is proprietary material of SECO S.p.A.

Unauthorized use, duplication, or modification by any means without prior consent of SECO S.p.A. is prohibited.

Every effort has been made to ensure the accuracy of this manual. However, SECO S.p.A. accepts no responsibility for any inaccuracies, errors or omissions herein. SECO S.p.A. reserves the right to change precise specifications without prior notice to supply the best product possible.

For further information on this module or other SECO products, but also to get the required assistance for any and possible issues, please contact us using the dedicated web form available at http://www.seco.com (registration required).

Our team is ready to assist.

## INDEX

| napter 1. INTRODUCTION                            | 5  |

|---------------------------------------------------|----|

| .1 Warranty                                       | 6  |

| .2 Information and assistance                     | 7  |

| .3 RMA number request                             | 7  |

| .4 Safety                                         |    |

| .5 Electrostatic Discharges                       |    |

| .6 RoHS compliance                                |    |

| .7 Safety Policy                                  | 9  |

| .8 Terminology and definitions                    |    |

| .9 Reference specifications                       |    |

| hapter 2. OVERVIEW                                | 15 |

| .1 Introduction                                   |    |

| .2 Technical Specifications                       |    |

| .3 Electrical Specifications                      |    |

| 2.3.1 Power Consumption                           |    |

| 2.3.2 Power Rails meanings                        |    |

| .4 Mechanical Specifications                      |    |

| .5 Supported Operating Systems                    |    |

| .6 Block Diagram                                  |    |

| napter 3. CONNECTORS                              | 23 |

| .1 Introduction                                   |    |

| .2 Connectors description                         |    |

| 3.2.1 SMARC Connector                             |    |

| hapter 4. BIOS SETUP                              | 53 |

| .1 Aptio setup Utility                            |    |

| .2 Main setup menu                                |    |

| 4.2.1 System Language / System Date / System Time |    |

| .3 Advanced menu                                  |    |

| 4.3.1 CPU Configuration                           |    |

| 4.3.2      | Power & Performance                                     | 57 |

|------------|---------------------------------------------------------|----|

| 4.3.3      | PCH-FW Configuration                                    | 64 |

| 4.3.4      | Intel® Time Coordinated Computing                       |    |

| 4.3.5      | Trusted computing                                       | 67 |

| 4.3.6      | ACPI Settings                                           | 67 |

| 4.3.7      | Serial Port Console Redirection                         |    |

| 4.3.8      | AMI Graphic Output Protocol Policy<br>USB Configuration | 69 |

| 4.3.9      | USB Configuration                                       | 69 |

| 4.3.10     | Network Stack configuration                             | 70 |

| 4.3.11     | Network Stack configuration<br>NVMe configuration       | 70 |

| 4.3.12     | SDIO configuration                                      | 70 |

| 4.3.13     | Main Thermal Configuration                              | 71 |

| 4.3.14     | LVDS Configuration                                      |    |

| 4.3.15     | Embedded Controller                                     |    |

| 4.3.16     | RAM Disk Configuration                                  |    |

| 4.4 Chip   | oset menu                                               |    |

| 4.4.1      | System Agent (SA) Configuration                         | 76 |

| 4.4.2      | PCH-IO Configuration                                    | /8 |

| 4.5 Sec    | urity menu                                              | 86 |

| 4.5.1      | Secure Boot submenu                                     | 86 |

| 4.6 Boo    | t menu                                                  | 88 |

| 4.7 Sav    | e & Exit menu                                           | 89 |

| Chapter 5. | Appendices                                              |    |

| 5.1 The    | mal Design                                              | 91 |

## Chapter 1. INTRODUCTION

- Warranty

- Information and assistance

- RMA number request

- Safety

- Electrostatic Discharges

- RoHS compliance

- Terminology and definitions

- Reference specifications

## 1.1 Warranty

This product is subject to the Italian Law Decree 24/2002, acting European Directive 1999/44/CE on matters of sale and warranties to consumers.

The warranty on this product lasts for 1 year.

Under the warranty period, the Supplier guarantees the buyer assistance and service for repairing, replacing or credit of the item, at the Supplier's own discretion.

Shipping costs that apply to non-conforming items or items that need replacement are to be paid by the customer.

Items cannot be returned unless previously authorised by the supplier.

The authorisation is released after completing the specific ticketing procedure <u>https://support.seco.com/</u> (web RMA). The RMA authorisation number must be put both on the packaging and on the documents shipped with the items, which must include all the accessories in their original packaging, with no signs of damage to, or tampering with, any returned item.

The error analysis form identifying the fault type must be completed by the customer and has must accompany the returned item.

If any of the above-mentioned requirements for RMA is not satisfied, the item will be shipped back and the customer will have to pay any and all shipping costs.

Following a technical analysis, the supplier will verify if all the requirements, for which a warranty service applies, are met. If the warranty cannot be applied, the Supplier will calculate the minimum cost of this initial analysis on the item and the repair costs. Costs for replaced components will be calculated separately.

SECO offers Engineering Samples for early evaluation and development. Engineering Samples are sold "as-is" with no warranty of any kind, neither explicit nor implied. Here <u>https://www.seco.com/it/EngineeringSamplesPolicy</u> is defined the framework of SECO and customer responsibilities regarding Engineering Samples.

Warning! All changes or modifications to the equipment not explicitly approved by SECO S.p.A. could impair the equipment's functionality and could void the warranty

### 1.2 Information and assistance

What do I have to do if the product is faulty?

SECO S.p.A. offers the following services:

- SECO website: visit <u>http://www.seco.com</u> to receive the latest information on the product. In most of the cases it is possible to find useful information to solve the problem.

- SECO Sales Representative: the Sales Rep can help to determine the exact cause of the problem and search for the best solution.

- SECO Help-Desk: contact SECO Technical Assistance. A technician is at disposal to understand the exact origin of the problem and suggest the correct solution.

E-mail: technical.service@seco.com

Fax (+39) 0575 350210

- Repair center: it is possible to send the faulty product to the SECO Repair Centre. In this case, follow this procedure:

- o Returned items must be accompanied by a RMA Number. Items sent without the RMA number will be not accepted.

- Returned items must be shipped in an appropriate package. SECO is not responsible for damages caused by accidental drop, improper usage, or customer neglect.

Note: Please have the following information before asking for technical assistance:

- Name and serial number of the product;

- Description of Customer's peripheral connections;

- Description of Customer's software (operating system, version, application software, etc.);

- A complete description of the problem;

- The exact words of every kind of error message encountered.

## 1.3 RMA number request

To request an RMA number, please visit SECO's web-site. On the home page, please select "RMA Online" and follow the procedure described. An RMA Number will be sent within 1 working day (only for on-line RMA requests).

## 1.4 Safety

This board uses only extremely low voltages.

While handling the board, please use extreme caution to avoid any kind of risk or damages to electronic components.

Always switch the power off, and unplug the power supply unit, before handling the board and/or connecting cables or other boards.

Avoid using metallic components - like paper clips, screws and similar - near the board when connected to a power supply, to avoid short circuits due to unwanted contacts with other board components.

If the board has become wet, never connect it to any external power supply unit or battery.

Check carefully that all cables are correctly connected and that they are not damaged.

### 1.5 Electrostatic Discharges

This board, like any other electronic product, is an electrostatic sensitive device: high voltages caused by static electricity could damage some or all the devices and/or components on-board.

Whenever handling this product, ground yourself through an anti-static wrist strap. Placement of the board on an anti-static surface is also highly recommended.

## 1.6 RoHS compliance

This board is designed using RoHS compliant components and is manufactured on a lead-free production line. It is therefore fully RoHS compliant.

## 1.7 Safety Policy

In order to meet the safety requirements of EN62368-1:2014 standard for Audio/Video, information and communication technology equipment, the HALLEY module shall be:

- used inside a fire enclosure made of non-combustible material or V-1 material (the fire enclosure is not necessary if the maximum power supplied to the module never exceeds 100 W, even in worst-case fault);

- used inside an enclosure; the enclosure is not necessary if the temperature of the parts likely to be touched never exceeds 70 °C;

- installed inside an enclosure compliant with all applicable IEC 62368-1 requirements;

The manufacturer which includes a HALLEY module in his end-user product shall:

- verify the compliance with B.2 and B.3 clauses of the EN62368-1 standard when the module works in its own final operating condition

- Prescribe temperature and humidity range for operating, transport and storage conditions;

- Prescribe to perform maintenance on the module only when it is off and has already cooled down;

- Prescribe that the connections from or to the Module have to be compliant to ES1 requirements;

- The module in its enclosure must be evaluated for temperature and airflow considerations.

## 1.8 Terminology and definitions

| ACPI       | Advanced Configuration and Power Interface, an open industrial standard for the board's devices configuration and power management                                         |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AHCI       | Advanced Host Controller Interface, a standard which defines the operation modes of SATA interface                                                                         |

| API        | Application Program Interface, a set of commands and functions that can be used by programmers for writing software for specific Operating Systems                         |

| AVC        | Advanced Video Coding, a video compression standard, also known as H.264                                                                                                   |

| BIOS       | Basic Input / Output System, the Firmware Interface that initializes the board before the OS starts loading                                                                |

| CAN Bus    | Controller Area network, a protocol designed for in-vehicle communication                                                                                                  |

| DDC        | Display Data Channel, a kind of I2C interface for digital communication between displays and graphics processing units (GPU)                                               |

| DDR        | Double Data Rate, a typology of memory devices which transfer data both on the rising and on the falling edge of the clock.                                                |

| DP         | Display Port, a type of digital video display interface                                                                                                                    |

| eDP        | embedded Display Port, a type of digital video display interface developed especially for internal connections between boards and digital displays                         |

| GBE        | Gigabit Ethernet                                                                                                                                                           |

| Gbps       | Gigabits per second                                                                                                                                                        |

| GND        | Ground                                                                                                                                                                     |

| GPI/O      | General purpose Input/Output                                                                                                                                               |

| HEVC       | High Efficiency Video Coding, a video compression standard, also known as H.265                                                                                            |

| HD Audio   | High Definition Audio, most recent standard for hardware codecs developed by Intel® in 2004 for higher audio quality                                                       |

| HDMI       | High Definition Multimedia Interface, a digital audio and video interface                                                                                                  |

| I2C Bus    | Inter-Integrated Circuit Bus, a simple serial bus consisting only of data and clock line, with multi-master capability                                                     |

| 12S        | Inter-Integrated Circuit Sound, an audio serial bus protocol interface developed by Philips (now NXP) in 1986                                                              |

| JPEG/MJPEG | Joint Photographic Experts Group, standard method for lossy compression of digital images. Motion JPEG is a video compression format                                       |

| LAN        | Local Area Network                                                                                                                                                         |

| LPDDR4     | Low-Power Double Data Rate Synchronous Dynamic Random Access Memory, 4th generation                                                                                        |

| LVDS       | Low Voltage Differential Signalling, a standard for transferring data at very high speed using inexpensive twisted pair copper cables, usually used for video applications |

| Mbps       | Megabits per second                                                                                                                                                        |

| MIPI       | Mobile Industry Processor Interface alliance                                                                                                                               |

| MMC/eMMC   | MultiMedia Card / embedded MMC, a type of memory card, having the same interface as the SD card. The eMMC is the embedded version of                                       |

|            |                                                                                                                                                                            |

|        | the MMC. They are devices that incorporate the flash memories on a single BGA chip.                                                                                                      |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MPEG2  | Standard for the generic coding of moving pictures and associated audio information                                                                                                      |

| MVC    | Multiview Video Coding, a stereoscopic video coding standard for video compression                                                                                                       |

| N.A.   | Not Applicable                                                                                                                                                                           |

| N.C.   | Not Connected                                                                                                                                                                            |

| OpenCL | Open Computing Language, specifies programming languages for programming different devices and API                                                                                       |

| OpenGL | Open Graphics Library, an Open Source API dedicated to 2D and 3D graphics                                                                                                                |

| OpenVG | Open Vector Graphics, an Open Source API dedicated to hardware accelerated 2D vector graphics                                                                                            |

| OS     | Operating System                                                                                                                                                                         |

| PCI-e  | Peripheral Component Interface Express                                                                                                                                                   |

| PHY    | Abbreviation of Physical, it is the device implementing the Physical Layer of ISO/OSI-7 model for communication systems                                                                  |

| PWM    | Pulse Width Modulation                                                                                                                                                                   |

| PWR    | Power                                                                                                                                                                                    |

| RGMII  | Reduced Gigabit Media Independent Interface, a standard interface between the Ethernet Media Access Control (MAC) and the Physical Layer                                                 |

| (PHY)  |                                                                                                                                                                                          |

| SATA   | Serial Advance Technology Attachment, a differential full duplex serial interface for Hard Disks                                                                                         |

| SD     | Secure Digital, a memory card type                                                                                                                                                       |

| SDIO   | Secure Digital Input/Output, an evolution of the SD standard that allows the use of the same SD interface to drive different Input/Output devices, like cameras, GPS, Tuners and so on.  |

| SGET   | Standardization Group for Embedded Technologies                                                                                                                                          |

| SMARC  | Smart Mobility Architecture, a computer Module standard maintained by the SGET                                                                                                           |

| SM Bus | System Management Bus, a subset of the I2C bus dedicated to communication with devices for system management, like a smart battery and other power supply-related devices.               |

| SOC    | System-on-a-chip                                                                                                                                                                         |

| SPI    | Serial Peripheral Interface, a 4-Wire synchronous full-duplex serial interface which is composed of a master and one or more slaves, individually<br>enabled through a Chip Select line. |

| TBM    | To be measured                                                                                                                                                                           |

| TMDS   | Transition-Minimized Differential Signalling, a method for transmitting high speed serial data, normally used on DVI and HDMI interfaces                                                 |

| UART   | Universal Asynchronous Receiver-Transmitter, is an asynchronous serial interface where data format and transmission speed are configurable                                               |

| UEFI   | Unified Extensible Firmware Interface, a specification defining the interface between the OS and the board's firmware. It is meant to replace the original BIOS interface                |

- USB Universal Serial Bus

- VP8 Open video compression format, a traditional block-based transform coding format

- VP9 Successor to VP8, customized for video greater than 1080p

- WMV9 Series 9 of Windows Media Video, a video compression format inlcuding native support for interlaced video, non-square pixels, and frame interpolation

## 1.9 Reference specifications

Here below it is a list of applicable industry specifications and reference documents.

| Reference                                                | Link                                                                                                                       |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| ACPI                                                     | https://uefi.org/specifications                                                                                            |

| AHCI                                                     | http://www.intel.com/content/www/us/en/io/serial-ata/ahci.html                                                             |

| CAN Bus                                                  | http://www.bosch-semiconductors.de/en/ubk_semiconductors/safe/ip_modules/can_literature/can_literature.html                |

| DDC                                                      | http://www.vesa.org                                                                                                        |

| DP, eDP                                                  | http://www.vesa.org                                                                                                        |

| FastEthernet                                             | http://standards.ieee.org/about/get/802/802.3.html                                                                         |

| Gigabit Ethernet                                         | https://standards.ieee.org/standard/802_3-2018.html                                                                        |

| HD Audio                                                 | http://www.intel.com/content/dam/www/public/us/en/documents/product-specifications/high-definition-audio-specification.pdf |

| HDMI                                                     | http://www.hdmi.org/index.aspx                                                                                             |

| I2C                                                      | http://www.nxp.com/documents/other/UM10204_v5.pdf                                                                          |

| I2S                                                      | https://www.sparkfun.com/datasheets/BreakoutBoards/I2SBUS.pdf                                                              |

| Intel <sup>®</sup> Atom <sup>™</sup> Elkhart Lake family | https://ark.intel.com/content/www/us/en/ark/products/codename/80644/Elkhart-lake.html#@Embedded                            |

| LVDS                                                     | http://www.ti.com/ww/en/analog/interface/lvds.shtml and http://www.ti.com/lit/ml/snla187/snla187.pdf                       |

| MIPI                                                     | http://www.mipi.org                                                                                                        |

| MMC/eMMC                                                 | http://www.jedec.org/committees/jc-649                                                                                     |

| OpenGL                                                   | http://www.opengl.org                                                                                                      |

| OpenVG                                                   | http://www.khronos.org/openvg                                                                                              |

| PCI Express                                              | http://www.pcisig.com/specifications/pciexpress                                                                            |

| SATA                                                     | https://www.sata-io.org                                                                                                    |

| SMARC Design Guide 2.0                                   | https://sget.org/wp-content/uploads/2018/09/SMARC_DG_V2.pdf                                                                |

| SMARC Hardware Specification 2.1.1                       | https://sget.org/wp-content/uploads/2020/05/SMARC_V211.pdf                                                                 |

| SD Card Association                                      | https://www.sdcard.org/home                                                                                                |

| SDIO                | https://www.sdcard.org/developers/overview/sdio                                      |

|---------------------|--------------------------------------------------------------------------------------|

| SM Bus              | http://www.smbus.org/specs                                                           |

| TMDS                | http://www.siliconimage.com/technologies/tmds                                        |

| UEFI                | http://www.uefi.org                                                                  |

| USB 2.0 and USB OTG | http://www.usb.org/developers/docs/usb_20_070113.zip                                 |

| USB 3.0             | https://usb.org.10-1-108-210.causewaynow.com/sites/default/files/usb_32_20191024.zip |

## Chapter 2. OVERVIEW

- Introduction

- Technical Specifications

- Electrical Specifications

- Mechanical Specifications

- Supported Operating Systems

- Block Diagram

## 2.1 Introduction

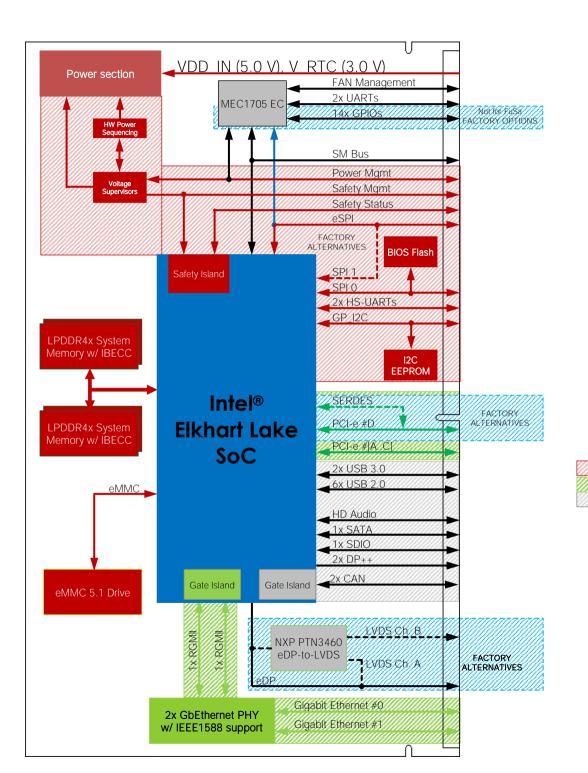

HALLEY is a SMARC Rel. 2.1.1 compliant module based on the Intel<sup>®</sup> Atom<sup>®</sup> x6000E Series and Intel<sup>®</sup> Pentium<sup>®</sup> and Celeron<sup>®</sup> N and J Series processors (formerly Elkhart Lake) for FuSa applications, a series of Dual / Quad SOCs with 64-bit instruction set.

These new family of processors offers different use conditions, such as PC Client, Embedded and Industrial targets and is optimized for usage in vertical applications for IOT including Industrial, Office Automation, Retail, Gaming, Healthcare, Transportation.

New features introduced by Elkhart Lake are, but not limited to the following: Time Sensitive Network (TSN) and Time Coordinate Computing (TCC) for real-time and responsive applications, Scalability and consolidation of temporally deterministic workloads, In band and OOB remote manageability (reboot/power-on/power-off), Platform Trust Technology (PTT), Dynamic Application Loader (DAL) and Secure Guard Extension (SGX), Intel Programmable Service Engine, Intel UHD Graphics, media, and display supporting, Fully Integrated Voltage Regulator (FIVR). Last but not least, this is the first Intel product designed with functional safety capabilities, made available by Intel<sup>®</sup> Safety Island (SI), a functional safety IP integrated into the Elkhart Lake Platform Control Hub (PCH), intended to raise the safety level of the platform with a single source for managing the safety faults of the SOC.

These SOCs embed all the features usually obtained by combination of CPU + platform Controller hubs, all in one single IC, which allows, therefore, the system minimisation and performance optimisation, which is essential for boards with sizes so reduced as for SMARC ("Smart Mobility ARChitecture") form factor, offering the computing abilities of a standard board, with the possibilities of combining with a ready-to-use carrier board like the SECO CSM-B79 or customised carrier board.

The Embedded Memory Controller allows the integration of up to 16GB of LPDDR4 Memory directly soldered onboard with In-Band Error Correction Code supported (Safety related feature) and speed up to 4267MT/s on single rank and 3733MT/s on dual rank.

All SOCs embed an Intel<sup>®</sup> Gen11 UHD Graphics controller with up to 32 Execution Units, which offer high graphical performances, with support for Microsoft<sup>®</sup> DirectX12.1, OpenGL 4.5, OpenCL<sup>™</sup> 1.2, OpenGL ES 3.1, Vulkan 1.1 and HW acceleration for video encoding and decoding of HEVC (H.265), H.264, VP8, VP9, JPEG/MJPEG. It is also possible the HW video decoding only of MPEG2, VC-1.

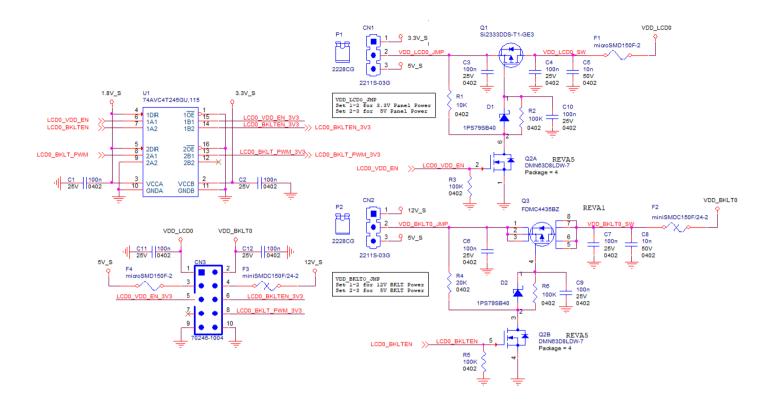

This embedded GPU is able to drive three independent displays, by using the interfaces available on SMARC connector: one DP++ 1.4, one HMDI 1.4 or DP++ 1.4 and one eDP 1.3 or Dual Channel 18/24bit LVDS (factory alternatives).

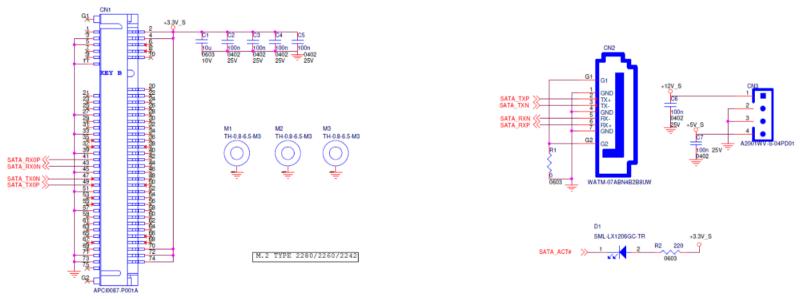

Mass Storage capabilities of the board include one external S-ATA Gen3 channel, a standard 4-bit SD interface and one optional eMMC 5.1 Drive soldered on board (Safety related), with up to 128GB capabilities.

Other than the interfaces already discussed previously, on SMARC connector there are the signals necessary for the implementation of 2x GbE, up to 6 ports in USB2.0 only and up to 2 Super Speed (SS) ports (i.e. USB 3.1 Gen2 compliant), 4 x PCI-Express Gen3 lanes, HD and I<sup>2</sup>S Audio interfaces, CAN, I<sup>2</sup>C, SPI and SM buses, up to 14 GPIOs, HS-UART and UART interfaces.

Interfacing to the board comes through a single card edge connector, whose pinout is defined by SMARC specifications Rel.2.1.1. For external interfacing to standard devices, a carrier board with a 230-pin MXM connector is needed. This board will implement all the routing of the interface signals to external standard connectors, as well as integration of other peripherals/devices not already included in HALLEY CPU module.

Please refer to following chapter for a complete list of all peripherals integrated and characteristics.

## 2.2 Technical Specifications

#### Processors

Intel<sup>®</sup> Atom<sup>™</sup> x6000E CPUs certified for FuSa, compliant to IEC 61508 and ISO 13849 requirements for Functional Safety and Safety Integrity Levels:

- Atom<sup>™</sup> x6427FE Quad Core @1.9GHz (no Turbo) 12W TDP w/ IBECC, IHS and TCC, FuSa Certified - Ind. Temp. Range

- Atom<sup>™</sup> x6200FE Dual Core @1.0GHz (no Turbo) 4.5W TDP no Graphics w/ IBECC, IHS and TCC, FuSa Certified- Ind. Temp. Range

Other Intel Atom<sup>™</sup> x6000E, Pentium<sup>®</sup> and Celeron<sup>®</sup> N and J Series CPUs:

- Celeron® J6413 Quad Core @ 1.8GHz (3.0GHZ Turbo) 10W TDP Comm. Temp. Range

- Celeron<sup>®</sup> N6211 Dual Core @1.2GHz (3.0GHZ Turbo) 6.5W TDP Comm. Temp. Range

- Pentium<sup>®</sup> J6426 Quad Core @2.0GHz (3.0GHZ Turbo) 10W TDP Comm. Temp. Range

- Pentium<sup>®</sup> N6415 Quad Core @1.2GHz (3.0GHZ Turbo) 6.5W TDP Comm. Temp. Range

- Atom<sup>™</sup> x6211E Dual Core @1.3GHz (3.0GHZ Turbo) 6W TDP w/ IBECC and IHS -Ind. Temp. Range

- Atom<sup>™</sup> x6413E Quad Core @1.5GHz (3.0GHZ Turbo) 9W TDP w/ IBECC and IHS -Ind. Temp. Range

- Atom™ x6425E Quad Core @2.0GHz (3.0GHZ Turbo) 12W TDP w/ IBECC and IHS

Ind. Temp. Range

- Atom<sup>™</sup> x6212RE Dual Core @1.2GHz (no Turbo) 6W TDP w/ IBECC, IHS and TCC

Ind. Temp. Range

- Atom<sup>™</sup> x6414RE Quad Core @1.5GHz (no Turbo) 9W TDP w/ IBECC, IHS and TCC

Ind. Temp. Range

- Atom<sup>™</sup> x6425RE Quad Core @1.9GHz (no Turbo) 12W TDP w/ IBECC, IHS and TCC - Ind. Temp. Range

(\*) IHS: Integrated Heatspreader; TCC: Time Coordinated Computing

#### Memory

32-bit LPDDR4x Soldered Down Memory

HALLEY

Up to 16GB Quad Channel with In-Band Error Correction Code (IBECC, Safety Related feature) supported 4GB Dual Channel, 8GB or 16GB Quad Channel

Speed:4267MT/s single rank (1GB/2GB/4GB/8GB), 3733MT/s dual rank (16GB)

#### Graphics

Up to 3 independent displays Integrated Gen11 UHD Graphics controller with up to 32 EU 4K HW decoding and encoding of HEVC (H.265), H.264, VP8/ VP9, WMV9/VC1 (decoding only) DirectX 12.1, OpenGL ES 3.1, OpenGL 4.5, OpenCL <sup>™</sup> 1.2, Vulkan 1.0

#### Video Interfaces

eDP 1.3 or Dual Channel 18/24bit LVDS interface (factory options)  $2 \times DP_{++} 1.4$  or  $1 \times DP_{++} 1.4$  and  $1 \times HDMI 1.4$  interfaces

#### Video Resolution

Up to 4096 x 2160 @60Hz

#### Mass Storage

1 x external S-ATA Gen3 Channel

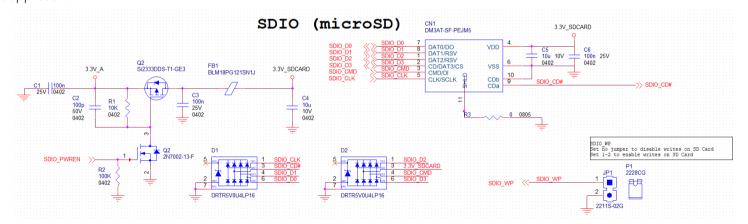

SDIO interface

Optional eMMC 5.1 drive soldered on-board (Safety Related)

PCI Express

Up to 4 x PCI-e Gen3 Lanes

#### Networking

2x Gigabit Ethernet PHY with precision clock synchronization and synchronous Ethernet clock output for IEEE 1588 (Safety Related – Black channel). Optional SERDES (SGMII) Interface for additional third Gigabit Ethernet (factory option, alternative to fourth PCI-e lane)

#### USB

6 x USB 2.0 Host Ports 2 x USB 3.1 Gen2 Ports

#### Audio

HD Audio interface

#### Serial ports

2 x HS-UARTs (Safety Related) 2 x UARTs

#### CAN Bus

2 x CAN interfaces

#### Other Interfaces

Up to 14x GPIOs SM Bus Power Management Signals I2C Bus 1x SPI interface for boot 1x General Purpose SPI or eSPI (Factory Alternatives)

#### Functional Safety Features

FuSa Interface signals for IEC 61508 and ISO 13849

Power supply voltage:  $+5V_{DC}$  and  $+3.3V_{RTC}$

#### Operating System

Microsoft<sup>®</sup> Windows 10 Enterprise (64 bit) Linux Yocto 64-bit Operating temperature:

Commercial version  $0^{\circ}C \div +60^{\circ}C^{**}$ . Industrial version  $-40^{\circ}C \div +85^{\circ}C^{**}$ .

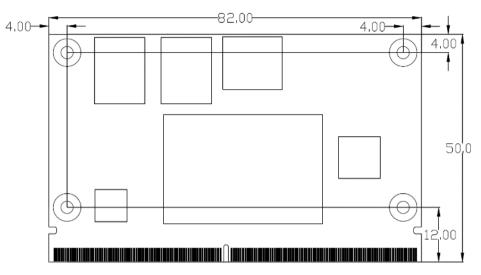

Dimensions: 50 x82 mm (1.97" x 3.23")

\*\* Measured at any point of SECO standard heatspreader for this product, during any and all times (including start-up). Actual temperature will widely depend on application, enclosure and/or environment. Upon customer to consider application-specific cooling solutions for the final system to keep the heatspreader temperature in the range indicated. Please also check paragraph 5.1

## 2.3 Electrical Specifications

According to SMARC specifications, the HALLEY module needs to be supplied only with an external +5V<sub>DC</sub> power supply.

For Real Time Clock working and CMOS memory data retention, it is also needed a backup battery voltage. All these voltages are supplied directly through card edge fingers (see connector's pinout). All remaining voltages needed for board's working are generated internally from +5V<sub>DC</sub> power rail.

#### 2.3.1 Power Consumption

HALLEY module, like all SMARC modules, needs a carrier board for its normal working. All connections with the external world come through this carrier board, which provide also the required voltage to the board, deriving it from its power supply source. Anyway, it has been possible to measure power consumption directly on VDD\_IN power rail (5V<sub>DC</sub>) that supplies the board. Power consumption must be intended as average value (30 seconds acquisition).

| Configur                                                 |                                                                                                                            |       |        |                                                                                                                             |        |       |                                                                                                                           | uration |        |                                                                                                                                  |        |       |        |       |        |       |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------|--------|-----------------------------------------------------------------------------------------------------------------------------|--------|-------|---------------------------------------------------------------------------------------------------------------------------|---------|--------|----------------------------------------------------------------------------------------------------------------------------------|--------|-------|--------|-------|--------|-------|

| Status                                                   | Intel Atom <sup>™</sup> x6425E<br>16GB LPDDR4<br>128GB eMMC<br>4 x PCI-e<br>LVDS and 2x DP++<br>TPM 2.0<br>Comm Temp Range |       |        | Intel Pentium <sup>®</sup> J6425<br>8GB LPDDR4<br>128GB eMMC<br>4 x PCI-e<br>LVDS and 2x DP++<br>TPM 2.0<br>Comm Temp Range |        |       | Intel Atom <sup>™</sup> x6425RE<br>16GB LPDDR4<br>128GB eMMC<br>4 x PCI-e<br>eDP and 2x DP++<br>TPM 2.0<br>Ind Temp Range |         |        | Intel Atom <sup>™</sup> x6427FE<br>8GB LPDDR4<br>64GB eMMC<br>4 x PCI-e<br>LVDS and 2x DP++<br>TPM 2.0<br>FuSa<br>Ind Temp Range |        |       |        |       |        |       |

|                                                          | Avg V                                                                                                                      | alue  | Peak V | /alue                                                                                                                       | Avg V  | alue  | Peak V                                                                                                                    | /alue   | Avg V  | alue                                                                                                                             | Peak \ | /alue | Avg V  | alue  | Peak V | /alue |

| ldle – (Win10) –<br>power saving<br>configuration        | 3.5W                                                                                                                       | 0.7A  | 6.22W  | 1.24A                                                                                                                       | 2.46W  | 0.49A | 6.79W                                                                                                                     | 1.35A   | 6W     | 1.2A                                                                                                                             | 6.3W   | 1.26A | 6.97W  | 1.39A | 9.71W  | 1.94A |

| OS Boot – (Win10)                                        | 5.68W                                                                                                                      | 1.13A | 12.63W | 2.52A                                                                                                                       | 6.28W  | 1.25A | 9.41W                                                                                                                     | 1.88A   | 7.85W  | 1.57A                                                                                                                            | 13.6W  | 2.72A | 6.83W  | 1.36A | 12.61W | 2.52A |

| Video reproduction<br>@1080p                             | 4.34W                                                                                                                      | 0.54A | 9.96W  | 2A                                                                                                                          | 4.27W  | 0.85A | 11W                                                                                                                       | 2.2A    | 6.53W  | 1.31A                                                                                                                            | 9.12W  | 1.82A | 7.38W  | 1.47A | 9.49W  | 1.9A  |

| Video reproduction<br>4K                                 | 6.71W                                                                                                                      | 1.34A | 10.64W | 2.12A                                                                                                                       | 6W     | 1.2A  | 11.83W                                                                                                                    | 2.36A   | 7.76W  | 1.55A                                                                                                                            | 10.47W | 2.09A | 7.76W  | 1.55A | 10.47A | 2.09A |

| Intel PTU (package<br>power limit and<br>TURBO Enabled)  | 16.12W                                                                                                                     | 3.22A | 19.96W | 3.98A                                                                                                                       | 11.22W | 2.24A | 16.29W                                                                                                                    | 3.25A   | 13.68W | 2.73A                                                                                                                            | 14.52W | 2.9A  | 13.39W | 2.68A | 14.03W | 2.8A  |

| Intel PTU (without<br>power limits and<br>TURBO Enabled) | 22.91W                                                                                                                     | 4.58A | 24.2W  | 4.83A                                                                                                                       | 17.36W | 3.47A | 18.92W                                                                                                                    | 3.98A   | 14.46W | 2.89A                                                                                                                            | 15.74W | 3.15A | 14.39W | 2.87A | 15.6W  | 3.12A |

Independently by the SOC mounted onboard, the following power consumptions are common to all boards:

| Battery Backup power consumption: | 3.11µA |

|-----------------------------------|--------|

| Soft-Off State power consumption: | 174mA  |

| Suspend State power consumption:  | 176mA  |

#### 2.3.2 Power Rails meanings

In all the tables contained in this manual, Power rails are named with the following meaning:

VDD\_IN: Module power input voltage. +5V voltage directly coming from the card edge connector, internally named as 5V\_DSW.

VDD\_RTC: Low current RTC circuit backup power. 3V coin cell voltage coming from the edge card for supplying the RTC clock on the Elkhart Lake SOCs.

+3.3V\_DSW: +3.3 Deep Sleep Well, derived internally from 5V\_DSW

+3.3V\_RUN: +3.3 Switched voltage, derived internally from +3.3V\_DSW

+3.3V\_ALW: +3.3 Always-on voltage, derived internally from +3.3V\_DSW

+1.8V\_ALW: +1.8 Always-on voltage, derived internally from 5V\_DSW

+1.8V\_RUN: +1.8 Switched voltage, derived internally from +1.8V\_ALW

+1.8V\_DSW: +1.8 Deep sleep well, derived internally from +3.3V\_DSW

## 2.4 Mechanical Specifications

According to SMARC<sup>®</sup> specifications, the board dimensions are: 50 x 82 mm (1.97" x  $^{-2}$  3.23") including the pin numbering and edge finger pattern.

Printed circuit of the board is made of twelve layers, some of them are ground planes, for disturbance rejection.

The MXM connector accommodates various connector heights for different carrier board applications needs.

When using different connector heights, please consider that, according to SMARC specifications, components placed on bottom side of the module will have a maximum height of 1.3mm. Keep this value in mind when choosing the MXM connector's height, if there is the need to place components on the carrier board in the area below the SMARC module.

### 2.5 Supported Operating Systems

HALLEY module supports the following operating systems:

- Microsoft<sup>®</sup> Windows 10 Enterprise (64 bit)

- Linux Yocto 64-bit

SECO will offer the BSP (Board Support Package) for these O.Ss, to reduce at minimum SW development of the board, supplying all the drivers and libraries needed for use both with the SMARC board and the Carrier Board, assuming that the Carrier Board is designed following SECO SMARC Design Guide, with the same IC's. For further details, please visit <a href="https://www.seco.com">https://www.seco.com</a>.

## 2.6 Block Diagram

## Chapter 3. CONNECTORS

- Introduction

- Connectors description

## 3.1 Introduction

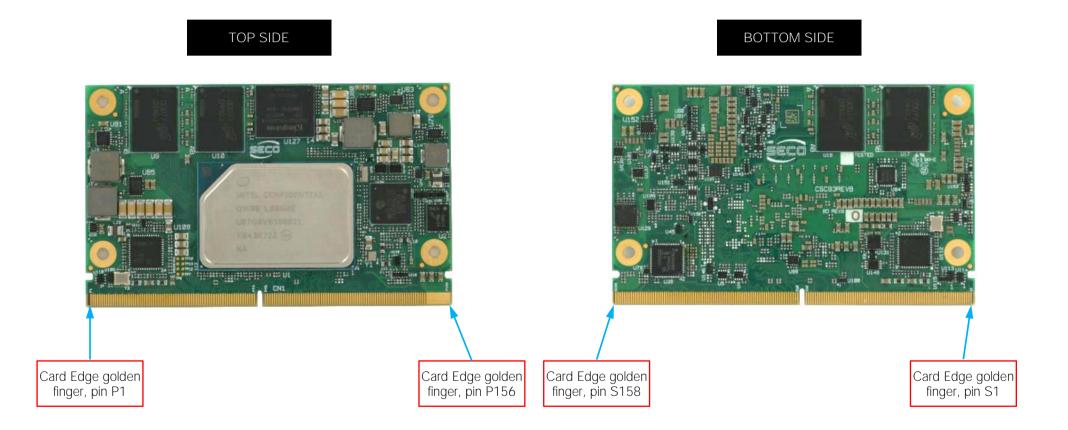

According to SMARC specifications, all interfaces to the board are available through a single card edge connector.

## 3.2 Connectors description

#### 3.2.1 SMARC Connector

According to SMARC Rel 2.1 specification, all interface signals are reported on the card edge connector, which is a 314-pin Card Edge that can be inserted into standard low profile 314 pin 0.5mm right pitch angle connector that was originally defined for use with MXM3 graphics cards.

Not all signals contemplated in the SMARC Rel 2.1 are implemented on card edge connector, therefore, please refer to the following table for a list of effective signals reported on the card edge connector.

For accurate signals description, please consult the following paragraphs.

| SMARC Golden Finger Connector – CN1 |      |            |         |         |               |           |              |

|-------------------------------------|------|------------|---------|---------|---------------|-----------|--------------|

|                                     | TO   | P SIDE     |         |         | BC            | TTOM SIDE |              |

| SIGNAL GROUP                        | Туре | Pin name   | Pin nr. | Pin nr. | Pin name      | Туре      | SIGNAL GROUP |

|                                     |      |            |         | S1      | PROCHOT       | I/O       | FUSA         |

| MANAGEMENT                          | Ι    | SMB_ALERT# | P1      | S2      | FUSA_PWRFAIL# | I/O       | FUSA         |

|                                     |      | GND        | P2      | S3      | GND           |           |              |

|                                     |      | N.C.       | P3      | S4      | CHXPMICEN     | I         | FUSA         |

|                                     |      | N.C        | P4      | S5      | N.C.          |           |              |

| GBE                                 | I/O  | GBE1_SDP   | P5      | S6      | N.C.          |           |              |

| GBE                                 | I/O  | GBE0_SDP   | P6      | S7      | N.C.          |           |              |

|                                     |      | N.C.       | P7      | S8      | N.C.          |           |              |

|                                     |      | N.C        | P8      | S9      | N.C.          |           |              |

|                                     |      | GND        | P9      | S10     | GND           |           |              |

|                                     |      | N.C.       | P10     | S11     | N.C.          |           |              |

|                                     |      | N.C        | P11     | S12     | N.C.          |           |              |

|                                     |      | GND        | P12     | S13     | GND           |           |              |

|                                     |      | N.C.       | P13     | S14     | N.C.          |           |              |

|                                     |      | N.C        | P14     | S15     | N.C.          |           |              |

|                                     |      | GND        | P15     | S16     | GND           |           |              |

|                                     |      | N.C.       | P16     | S17     | GBE1_MDI0+    | I/O       | GBE          |

|                 |     | N.C            | P17 | S18 | GBE1_MDI0-                   | I/O | GBE            |

|-----------------|-----|----------------|-----|-----|------------------------------|-----|----------------|

|                 |     | GND            | P18 | S19 | GBE1_LINK100#                | 0   |                |

| GBE             | I/O | GBE0_MDI3-     | P19 | S20 | GBE1_MDI1+                   | I/O | GBE            |

| GBE             | I/O | GBE0_MDI3+     | P20 | S21 | GBE1_MDI1-                   | I/O | GBE            |

| GBE             | 0   | GBE0_LINK100#  | P21 | S22 | GBE1_LINK1000#               | 0   |                |

| GBE             | 0   | GBE0_LINK1000# | P22 | S23 | GBE1_MDI2+                   | I/O | GBE            |

| GBE             | I/O | GBE0_MDI2-     | P23 | S24 | GBE1_MDI2-                   | I/O | GBE            |

| GBE             | I/O | GBE0_MDI2+     | P24 | S25 | GND                          |     |                |

| GBE             | 0   | GBE0_LINK_ACT# | P25 | S26 | GBE1_MDI3-                   | I/O | GBE            |

| GBE             | I/O | GBE0_MDI1-     | P26 | S27 | GBE1_MDI3+                   | I/O | GBE            |

| GBE             | I/O | GBE0_MDI1+     | P27 | S28 | N.C.                         |     |                |

|                 |     | N.C.           | P28 | S29 | SERDES_0_TX+ /<br>PCIE_D_TX+ | 0   | SERDES / PCI-e |

| GBE             | I/O | GBE0_MDI0-     | P29 | S30 | SERDES_0_TX- /<br>PCIE_D_TX- | 0   | SERDES / PCI-e |

| GBE             | I/O | GBE0_MDI0+     | P30 | S31 | GBE1_LINK_ACT#               | 0   | GBE            |

|                 |     | N.C.           | P31 | S32 | SERDES_0_RX+ /<br>PCIE_D_RX+ | I   | SERDES / PCI-e |

|                 |     | GND            | P32 | S33 | SERDES_0_RX- /<br>PCIE_D_RX- | I   | SERDES / PCI-e |

| SDIO_CARD       |     | SDIO_WP        | P33 | S34 | GND                          |     |                |

| SDIO_CARD       | I/O | SDIO_CMD       | P34 | S35 | USB4+                        | I/O | USB            |

| SDIO_CARD       | Ι   | SDIO_CD#       | P35 | S36 | USB4-                        | I/O | USB            |

| SDIO_CARD       | 0   | SDIO_CK        | P36 | S37 | N.C.                         |     |                |

| SDIO_CARD       | 0   | SDIO_PWR_EN    | P37 | S38 | AUDIO_MCK                    | 0   | AUDIO          |

|                 |     | GND            | P38 | S39 | I2SO_LRCK                    | I/O | AUDIO          |

| SDIO_CARD       | I/O | SDIO_DO        | P39 | S40 | I2S0_SDOUT                   | 0   | AUDIO          |

| SDIO_CARD       | I/O | SDIO_D1        | P40 | S41 | I2S0_SDIN                    | I   | AUDIO          |

| SDIO_CARD       | I/O | SDIO_D2        | P41 | S42 | I2S0_CK                      | I/O | AUDIO          |

| SDIO_CARD       | I/O | SDIO_D3        | P42 | S43 | ESPI_ALERTO#                 | I   | ESPI INTERFACE |

| SPI 0 INTERFACE | 0   | SPI0_CS0#      | P43 | S44 | ESPI_ALERT1#                 | Ι   | ESPI INTERFACE |

| SPI O INTERFACEQSPIQ_CKP44S46MDIO_COLKQSLRDESSPIO INTERFACEISPIQ_DONP46S47GNDW/OSERDESSPIO INTERFACEISPIQ_DONP46S47GNDW/OIZCSATAQSATAP47S48IZC_GP_CKV/OIZCSATAQSATA,IX+P48S0VIDA_SYNCV/OVIDAUIOSATAQSATA,IX+P48S51HDA_SDOQHDA JUDIOSATAISATA,IX+P51S52HDA_CKOHDA JUDIOSATAISATA,RX+P51S53HDA_CKOSATASATAISATA,RX+P53S54SATA_ACT#OSATASPI 1/SO/FENICESE/CSOFP54S55USB5U/OU/OUSBSPI 1/SO/FENICESE/CSOFP54S56USB5U/OSPIINTEFACESPI 1/SO/FENICESE/CSOFP54S56USB5U/OU/OUSBSPI 1/SO/FENICESE/CSOFP54S56USB5U/OU/OUSBSPI 1/SO/FENICESE/CSOFP54S57USB5U/OU/OUSBSPI 1/SO/FENICESE/CSOFP54S56USB5U/OU/OUSBSPI 1/SO/FENICESE/CSOFP54S57USB5U/OU/OUSBSPI 1/SO/FENICESE/CSOFP54S57USB5U/OU/OU/OSPI 1/SO/FENICESE/CSOFP51S56USB5U/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |     |                      |     |     |             |     |                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|----------------------|-----|-----|-------------|-----|----------------|

| SPI 0 INTERFACE         O         SPD DO         P46         S47         GND           SATA         O         SATA_TX+         P47         S48         !2C_GF_CK         I/O         !2C           SATA         O         SATA_TX+         P48         S49         !2C_GP_DAT         V/O         !2C           SATA         O         SATA_TX-         P48         S49         !DA_SYNC         V/O         !DAUDIO           SATA         O         SATA_TX-         P48         S50         !HDA_SYNC         V/O         !HDAUDIO           SATA         I         SATA_TX+         P51         S51         !HDA_SDO         O         !HDAUDIO           SATA         I         SATA_TX+         P51         S52         !HDA_SDI         I         HDAUDIO           SATA         I         SATA_TX+         P52         S53         !HDA_SDI         I         HDAUDIO           SATA         I         SATA_TX+         P52         S55         !S51_D_C2#         !O         !SATA           SPI 1 / cSPIINTERFACE         O         SPI_D_CS0#/ESPLCS0#         P54         S55         !S51_D_C2#         !O         SPIINTERFACE           SPI 1 / cSPIINTERFACE         I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SPI 0 INTERFACE        | 0   | SPIO_CK              | P44 | S45 | MDIO_CLK    | 0   | SERDES         |

| ATAGNDP47S48I2C_GP_CKV0I2CSATAOSATA_TX+P48S49I2C_GP_DATV0I2CSATAOSATA_TX+P49S50HDA_SYNCV0HDAUDIOSATAISATA_RX+P50S51HDA_SDOOHDAUDIOSATAISATA_RX+P51S52HDA_SDOOHDAUDIOSATAISATA_RX+P51S52HDA_CKOSATASPI 1/ SPIINTERFACEISATA_RX+P52S53HDA_CKOSATASPI 1/ SPIINTERFACESPII_CS/#/FSPI_CS/#P55S56FSPI_O_2VOSSFSPI 1/ SPIINTERFACESPII_CS/#/FSPI_CS/#P55S56FSPI_Q2VOSSFSPI 1/ SPIINTERFACESPII_CS/#/FSPI_CS/#P55S56FSPI_Q2VOSSFSPI 1/ SPIINTERFACESPII_CS/#/FSPI_CS/#P55S56FSPI_Q2VOSSFSPI 1/ SPIINTERFACESPII_CS/#/FSPI_CS/#P55S56FSPI_Q2VOSSFSPI 1/ SPIINTERFACESPII_CS/#/FSPI_CS/#P55S56FSPI_Q2VOSSFSPI 1/ SPIINTERFACEVOSPIINTERFACEP56S57ESPI_Q2VOSSFSPI 1/ SPIINTERFACESPII_CS/#/FSPI_CS/#P55S56FSPI_Q2VOVSSSPI 1/ SPIINTERFACESPII_CS/#/FSPI_CS/#P56S57ESPI_Q2VOVSSSPI 1/ SPI_DO/TSPI_O_1P57S58ESPI_STVO <td>SPI 0 INTERFACE</td> <td> </td> <td>SPIO_DIN</td> <td>P45</td> <td>S46</td> <td>MDIO_DAT</td> <td>I/O</td> <td>SERDES</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SPI 0 INTERFACE        |     | SPIO_DIN             | P45 | S46 | MDIO_DAT    | I/O | SERDES         |

| SATA0SATA_TX+P48S49I2C_GP_DATI/0I2CSATA0SATA_TX-P49S50HDA_SYNCI/0HD AUDIOSATACNDP50S51HDA_SDOOHD AUDIOSATA1SATA_RX+P50S52HDA_SDIIHD AUDIOSATA1SATA_RX+P52S53HDA_CKOHD AUDIOSTSATA_RX+P52S54SATA_CT#OSATASPI1/cSPIINTERFACE0SPI1_CSO#/SSPI.CSU#P54S55USB5_EN_OC#I/OUSBSPI1/cSPIINTERFACE0SPI1_CSC#/SSPI.CSU#P54S56ESPLO_2VOUSBSPI1/cSPIINTERFACE0SPI1_CSU#/SSPI.CSU#P56S56ESPLO_2VOUSBSPI1/cSPIINTERFACE0SPI1_CK/ESPI.CSU#P56S56ESPLO_2VOUSBSPI1/cSPIINTERFACE0SPI1_CK/ESPI.CSU#P57S58ESPLRESET#OeSPIINTERFACESPI1/cSPIINTERFACE10SPI1_DIV/ESPI.D_OP58S59USB5+VOUSBSPI1/cSPIINTERFACE100SS0P59S60USB5+VOUSBSPI1/cSPIINTERFACE100USB0_FN_OC#P61S62USB3_SSTX+OUSBUSBVOUSB0_FN_OC#P64S64GNDUSBUSBUSBUSBUSBVOUSB1_EN_OC#P64S64USB3_SSTX+IUSBUSBUSB <td< td=""><td>SPI 0 INTERFACE</td><td>0</td><td>SPIO_DO</td><td>P46</td><td>S47</td><td>GND</td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SPI 0 INTERFACE        | 0   | SPIO_DO              | P46 | S47 | GND         |     |                |

| SATA<br>C<br>MAO<br>MASATA_TX-<br>MAP49S50HDA_SYNCI/OHD AUDIOSATAI<br>MDSATA_RX+P50S51HDA_SDOOHD AUDIOSATAISATA_RX+P51S52HDA_CKOHD AUDIOSATAISATA_RX-P50S54SATA_CT#OSATASPI1STA_RX-P53S54SATA_CT#OSATASPI1/sSPINTERFACEOSPI_CS0#/ESPLCS0#P54S56ESPLO_2VOvSPINTERFACESPI1/sSPINTERFACESPI1_CS1#/SSPICS1#P55S56ESPLO_3VOeSPINTERFACESPI1/sSPINTERFACEVOSPINTERFACES70S58ESPLRSET#VOeSPINTERFACESPI1/sSPINTERFACEVOSPINTERFACEP59S58ESPLRSET#VOUSBSPI1/sSPINTERFACEVOSPINTERFACEP59S50USB5+VOUSBSPI1/sSPINTERFACEVOSPINTERFACEP59S60USB5+VOUSBSPI1/sSPINTERFACEVOSS0+P59S60USB5+VOUSBSPI1/sSPINTERFACEVOUSB0+P60S61GNDUSBUSBUSBVOUSB0+P60S61USB3_SSTX+OUSBUSBUSBVOUSB1_P64S67GNDUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                        |     | GND                  | P47 | S48 | I2C_GP_CK   | I/O | 12C            |

| GND         P50         S51         HDA_SDO         O         HD AUDIO           SATA         I         SATA_RX+         P51         S52         HDA_SDI         I         HD AUDIO           SATA         I         SATA_RX-         P52         S53         HDA_CK         O         HD AUDIO           SPI1 / eSPIINTERFACE         O         SATA_RX-         P52         S53         HDA_CK         O         SATA           SPI1 / eSPIINTERFACE         O         SATA_RX-         P52         S56         USB5_EN_OC#         VO         USB           SPI1 / eSPIINTERFACE         O         SPI1_CSO#/ESPI_CS1#         P55         S56         ESP_LIO_2         VO         ESPIINTERFACE           SPI1 / eSPIINTERFACE         VO         SPII_DIN / ESPI_O_1         P57         S58         ESP_LRESET#         O         eSPIINTERFACE           SPI1 / eSPIINTERFACE         VO         SPII_DO / FSP_O_0         P58         S59         USB5-         VO         USB           USB         GND         USB0         S91         USB5-         VO         USB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SATA                   | 0   | SATA_TX+             | P48 | S49 | I2C_GP_DAT  | I/O | 12C            |

| SATAISATA_RX+P51S52HDA_SDIIHD AUDOSATAISATA_RX-P52S53HDA_CKOHD AUDOSPICNDP53S54SATA_ACT#OSATASPI1/CS0#/ESPI_CS0#P54S56USB SE_N_OC#VOeSPIINTERFACESPI1/SD1/TERFACEOSPI1_CS1#/ESPL_CS1#P55S56ESPL_O_2VOeSPIINTERFACESPI1/SD1/TERFACEOSPI1_CS1#/ESPL_CS1#P56S57ESPL_O_3VOeSPIINTERFACESPI1/SD1/TERFACEVOSPII_DO / FSPL_O_1P57S58ESPL_RESET#OeSPIINTERFACESPI1/SD1/TERFACEVOSPI_DO / FSPL_O_0P58S59USB5-NOUSBSPI1/SD1/TERFACEVOSPI_DO / FSPL_O_0P58S59USB5-NVOUSBSPI1/SD1/TERFACEVOSPI_DO / FSPL_O_0P58S59USB5-NVOUSBSPI1/SD1/TERFACEVOSPI_DO / FSPL_O_0P58S59USB5-NVOUSBUSBVOUSB0-NP59S61USB5-NVOUSBUSBUSBVOUSB0-NP64S62USB_SSTX+0OUSBUSBUSBVOUSB1-NP64S64USB3_SSRX+1IUSBUSBUSBVOUSB1-NP64S64USB3_SSRX+1IUSBUSBUSBVOUSB1_NP64S64USB3_SSRX+1IUSBUSB<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SATA                   | 0   | SATA_TX-             | P49 | S50 | HDA_SYNC    | I/O | HD AUDIO       |

| SATA         I         SATA_RX-         P52         S53         HDA_CK         O         HD AUDIO           GND         P53         S54         SATA_ACT#         O         SATA           SPI1 / eSPIINTERFACE         O         SPI1_CSO#/ESPI_CSO#         P54         S55         USB5_EN_OC#         I/O         USB           SPI1 / eSPIINTERFACE         O         SPI1_CSO#/ESPI_CS1#         P55         S56         ESPI_O_2         I/O         eSPIINTERFACE           SPI1 / eSPIINTERFACE         VO         SPII_CK / ESPI_CS1#         P56         S57         ESPI_O_3         V/O         eSPIINTERFACE           SPI1 / eSPIINTERFACE         VO         SPII_DN / ESPI_O_1         P57         S58         ESPI_RESET#         O         eSPIINTERFACE           SPI1 / eSPIINTERFACE         VO         SPII_DO / ESPI_O_0         P58         S59         USB5-         V/O         USB           SPI1 / eSPIINTERFACE         VO         SBI         SS9         USB5-         V/O         USB           USB         VIO         USB0_EN_OC#         P60         S61         GND         USB         U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                        |     | GND                  | P50 | S51 | HDA_SDO     | 0   | HD AUDIO       |

| Index         P53         S54         SATA_ACT#         O         SATA           SP11/oSPIINTERFACE         O         SP11_CSO#/ESPL_CSO#         P54         S55         USB5_EN_OC#         VO         USB           SP11/oSPIINTERFACE         SP11_CSO#/ESPL_CSO#         P54         S56         ESPL_O_2         VO         eSPIINTERFACE           SP11/oSPIINTERFACE         O         SP11_CK / ESPL_OL         P56         S57         ESPL_O_3         VO         eSPIINTERFACE           SP11/oSPIINTERFACE         VO         SP11_DIN / ESPL_O_1         P57         S58         ESPL_RESET#         O         eSPIINTERFACE           SP11_oSPIINTERFACE         VO         SP11_DO / ESPL_O_0         P58         S59         USB5_EN_OC         VO         USB           SP11_OSPINTERFACE         VO         USB0         P59         S60         USB5_EN_OC         VO         USB           USB         VO         USB0+         P61         S62         USB3_SSTX+         O         USB         USB           USB         VO         USB0_EN_OC#         P62         S64         USB3_SSTX+         I         USB         USB           USB         VO         USB1_EN_OC#         P64         S65         U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SATA                   |     | SATA_RX+             | P51 | S52 | HDA_SDI     |     | HD AUDIO       |

| SP1 1 / eSP1 INTERFACE0SP11_CS0#/ESP1_CS0#P54S55USB5_EN_OC#V/OUSBSP1 1 / eSP1 INTERFACESP11_CS1#/ESP1_CS1#P55S56ESP1_0_2V/OeSP1 INTERFACESP1 1 / eSP1 INTERFACEOSP11_CK / ESP1_CKP56S57ESP1_0_3V/OeSP1 INTERFACESP1 1 / eSP1 INTERFACEV/OSP1_DIN / ESP1_0_1P57S58ESP_RESET#OeSP1 INTERFACESP1 1 / eSP1 INTERFACEV/OSP1_DIN / ESP1_0_0P58S59USB5+V/OUSBSP1 1 / eSP1 INTERFACEV/OSB1P59S60USB5+V/OUSBUSBUSBV/OUSB0NCS60USB3_SSTX+OUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSBUSB<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SATA                   | 1   | SATA_RX-             | P52 | S53 | HDA_CK      | 0   | HD AUDIO       |

| SP11 / eSP1 iNTERFACESP11 / eS1 #/ESP1_CS1#P55S56ESP1_0_2V/OeSP1 iNTERFACESP11 / eSP1 iNTERFACEVOSP11_CK / ESP1_CKP56S57ESP1_0_3V/OeSP1 iNTERFACESP11 / eSP1 iNTERFACEVOSP11_DIN / ESP1_0_0P58S59USB5+V/OUSBSP11 / eSP1 iNTERFACEVOSP1_0_0 / ESP1_0_0_0P58S50USB5+V/OUSBUSBVOUSB0+P60S61GNDUSBUSBUSBUSBVOUSB0+P60S61GNDUSBUSBUSBVOUSB0+P60S61GNDUSBUSBUSBVOUSB0+P60S61GNDUSBUSBUSBVOUSB0+P60S64USB_SSTX+OUSBUSBVOUSB0_EN_OC#P62S63USB3_SSTX+OUSBUSBVOUSB1+P63S64GNDUSBUSBUSBVOUSB1+P64S64USB3_SSTX+IUSBUSBVOUSB1-P66S67GNDUSBUSBUSBVOUSB1-P67S68USB3_SSTX+IUSBUSBVOUSB1-P68S69USB3_SV/OUSBUSBVOUSB2+P69S64USB3_STX+IUSBUSBVOUSB2+P69S64USB3_STX+IUSBUSBVOUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                        |     | GND                  | P53 | S54 | SATA_ACT#   | 0   | SATA           |

| SP1 1 / eSPI INTERFACEOSP11_CK / ESPI_CKP56S57ESPI_0_3I/OeSPI INTERFACESP1 1 / eSPI INTERFACEI/OSP11_DIN / ESPI_IO_1P57S58ESPI_RESET#OeSPI INTERFACESP1 1 / eSPI INTERFACEI/OSP11_DO / ESPI_IO_0P58S59USB5+I/OUSBSP1 1 / eSPI INTERFACEI/OSP11_DO / ESPI_IO_0P58S59USB5+I/OUSBUSBI/OUSB0+P59S60USB5-I/OUSBUSBI/OUSB0+P60S61GNDUSBUSBI/OUSB0-EN_OC#P61S62USB3_SSTX+OUSBUSBI/OUSB0_EN_OC#P63S64GNDUSBUSBUSBI/OUSB1+P63S64USB_SSTX+IUSBUSBI/OUSB1+P64S65USB_SSTX+IUSBUSBI/OUSB1+P65S64USB_SSTX+IUSBUSBI/OUSB1-EN_OC#P67S68USB3_STX+IUSBUSBI/OUSB1_EN_OC#P67S64USB3_I/OUSBUSBI/OUSB2_EN_OC#P67S64USB3_I/OUSBUSBI/OUSB2_STX+I/OUSBUSBI/OUSBUSBI/OUSB2_EN_OC#P69S70GNDUSBUSBI/OUSB2_EN_OC#P71S72USB2_STX+OUSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SPI 1 / eSPI INTERFACE | 0   | SPI1_CS0#/ESPI_CS0#  | P54 | S55 | USB5_EN_OC# | I/O | USB            |