# User Manual

# ETX-A61

ETX<sup>®</sup> 3.0 compliant module with the Intel<sup>®</sup> Atom<sup>™</sup> E3800 and Celeron<sup>®</sup> Bay Trail family SOCs

# www.seco.com

# **REVISION HISTORY**

| Revision | Date                           | Note                                                                                                                                                                                           | Rif |

|----------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.0      | 2 <sup>nd</sup> December 2015  | First Release                                                                                                                                                                                  | SB  |

| 1.1      | 26 <sup>th</sup> January 2016  | Minor corrections<br>BIOS Section updated                                                                                                                                                      | SB  |

| 1.2      | 7 <sup>th</sup> September 2017 | Industrial temperature removed from Technical features<br>ISA limitations added (par. 3.2.5.4.1)<br>Double PATA configuration reset workaround added (par. 3.2.5.10.1)<br>BIOS Section updated | SB  |

#### All rights reserved. All information contained in this manual is proprietary and confidential material of SECO S.r.l.

Unauthorised use, duplication, modification or disclosure of the information to a third-party by any means without prior consent of SECO S.r.l. is prohibited.

Every effort has been made to ensure the accuracy of this manual. However, SECO S.r.l. accepts no responsibility for any inaccuracies, errors or omissions herein. SECO S.r.l. reserves the right to change precise specifications without prior notice to supply the best product possible.

Some of the information found in the BIOS SETUP Chapter has been extracted from the following copyrighted Insyde Software Corp. documents:

• InsydeH2O<sup>™</sup> Setup Utility - User Reference Guide

The above mentioned documents are copyright © 2008 Insyde Software Corp. All rights reserved.

For further information on this module or other SECO products, but also to get the required assistance for any and possible issues, please contact us using the dedicated web form available at http://www.seco.com (registration required).

Our team is read to assist you.

# INDEX

| Chapter      | 1. INTRODUCTION             | 5   |

|--------------|-----------------------------|-----|

| 1.1          | Warranty                    | . 6 |

| 1.2          | Information and assistance  | . 7 |

| 1.3          | RMA number request          | . 7 |

| 1.4          | Safety                      | 8   |

| 1.5          | Electrostatic Discharges    | 8   |

| 1.6          | RoHS compliance             | 8   |

| 1.7          | Terminology and definitions | 9   |

| 1.8          | Reference specifications    |     |

| Chapter      | 2. OVERVIEW                 | 2   |

| 2.1          | Introduction                | 13  |

| 2.2          | Technical Specifications    | 4   |

| 2.3          | Electrical Specifications   | 15  |

| 2.3.         | 5                           |     |

| 2.3.         |                             |     |

| 2.4          | Mechanical Specifications   |     |

| 2.5          | Block Diagram               |     |

| Chapter      |                             |     |

| 3.1          | Introduction                |     |

| 3.2          | Connectors description      |     |

| 3.2.         |                             |     |

| 3.2.<br>3.2. |                             |     |

| 3.2.<br>3.2. |                             |     |

| 3.2.         |                             |     |

| Chapter      |                             |     |

| •            | InsydeH2O setup Utility     |     |

| 4.1          | Main setup menu             |     |

| 4.2          |                             |     |

| 1.2.         |                             | . 0 |

**SECO** ETX-A61 ETX-A61 User Manual - Rev. First Edition: 1.0 - Last Edition: 1.2 - Author: S.B. - Reviewed by G.G. Copyright © 2017 SECO S.r.l.

| 4.3 Ac     | dvanced menu                             |    |

|------------|------------------------------------------|----|

| 4.3.1      | Boot configuration submenu               |    |

| 4.3.2      | PCI Express configuration submenu        |    |

| 4.3.3      | USB configuration submenu                |    |

| 4.3.4      | Audio configuration submenu              |    |

| 4.3.5      | LPSS & SCC configuration submenu         |    |

| 4.3.6      | Miscellaneous Configuration submenu      | 51 |

| 4.3.7      | Security configuration submenu           |    |

| 4.3.8      | Video configuration submenu              |    |

| 4.3.9      | Chipset configuration submenu            |    |

| 4.3.10     | SATA configuration submenu               |    |

| 4.3.11     | Console Redirection submenu              |    |

| 4.3.12     | ACPI Table/features submenu              |    |

| 4.3.13     | Super I/O configuration submenu          |    |

| 4.3.14     | ······································   |    |

| 4.3.15     | 5                                        |    |

| 4.3.16     | LPC to ISA Bridge Configuration submenu  | 60 |

| 4.4 Se     | ecurity menu                             |    |

| 4.4.1      | USB Disk Signature Option submenu        | 61 |

| 4.5 Pc     | ower menu                                |    |

| 4.5.1      | Advanced CPU control submenu             |    |

| 4.5.2      | EC Watchdog Configuration submenu        |    |

| 4.5.3      | Thermal Zone configuration submenu       |    |

| 4.6 Bo     | oot menu                                 |    |

| 4.6.1      | Fixed Legacy Boot Order Settings Submenu |    |

| 4.6.2      | Legacy submenu                           |    |

| 4.7 Ex     | xit menu                                 |    |

| Chapter 5. | Appendices                               | 69 |

| 5.1 Th     | nermal Design                            |    |

# Chapter 1. INTRODUCTION

- Warranty

- Information and assistance

- RMA number request

- Safety

- Electrostatic Discharges

- RoHS compliance

- Terminology and definitions

- Reference specifications

# 1.1 Warranty

This product is subject to the Italian Law Decree 24/2002, acting European Directive 1999/44/CE on matters of sale and warranties to consumers. The warranty on this product lasts 1 year.

Under the warranty period, the Supplier guarantees the buyer assistance and service for repairing, replacing or credit of the item, at the Supplier's own discretion.

Shipping costs that apply to non-conforming items or items that need replacement are to be paid by the customer.

Items cannot be returned unless previously authorised by the supplier.

The authorisation is released after completing the specific form available on the web-site <u>http://www.seco.com</u> (RMA Online). The RMA authorisation number must be put both on the packaging and on the documents shipped with the items, which must include all the accessories in their original packaging, with no signs of damage to, or tampering with, any returned item.

The error analysis form identifying the fault type must be completed by the customer and must accompany the returned item.

If any of the above mentioned requirements for RMA is not satisfied, the item will be shipped back and the customer will have to pay any and all shipping costs.

Following a technical analysis, the supplier will verify if all the requirements for which a warranty service applies are met. If the warranty cannot be applied, the Supplier will calculate the minimum cost of this initial analysis on the item and the repair costs. Costs for replaced components will be calculated separately.

Warning! All changes or modifications to the equipment not explicitly approved by SECO S.r.l. could impair the equipment's functionality and could void the warranty

## 1.2 Information and assistance

What do I have to do if the product is faulty?

SECO S.r.l. offers the following services:

- SECO website: visit <u>http://www.seco.com</u> to receive the latest information on the product. In most of the cases it is possible to find useful information to solve the problem.

- SECO Sales Representative: the Sales Rep can help to determine the exact cause of the problem and search for the best solution.

- SECO Help-Desk: contact SECO Technical Assistance. A technician is at disposal to understand the exact origin of the problem and suggest the correct solution.

E-mail: technical.service@seco.com

Fax (+39) 0575 340434

- Repair centre: it is possible to send the faulty product to the SECO Repair Centre. In this case, follow this procedure:

- o Returned items must be accompanied by a RMA Number. Items sent without the RMA number will be not accepted.

- Returned items must be shipped in an appropriate package. SECO is not responsible for damages caused by accidental drop, improper usage, or customer neglect.

### Note: Please have the following information before requesting technical assistance:

- Name and serial number of the product;

- Description of Customer's peripheral connections;

- Description of Customer's software (operating system, version, application software, etc.);

- A complete description of the problem;

- The exact words of every kind of error message encountered.

# 1.3 RMA number request

To request a RMA number, please visit SECO's web-site. On the home page, please select "RMA Online" and follow the procedure described.

A RMA Number will be sent within 1 working day (only for on-line RMA requests).

# 1.4 Safety

The ETX-A61 module uses only extremely-low voltages.

While handling the board, please use extreme caution to avoid any kind of risk or damages to electronic components.

Always switch the power off, and unplug the power supply unit, before handling the board and/or connecting cables or other boards.

Avoid using metallic components - like paper clips, screws and similar - near the board when connected to a power supply, to avoid short circuits due to unwanted contacts with other board components.

If the board has become wet, never connect it to any external power supply unit or battery.

Check carefully that all cables are correctly connected and that they are not damaged.

## 1.5 Electrostatic Discharges

The ETX-A61 module, like any other electronic product, is an electrostatic sensitive device: high voltages caused by static electricity could damage some or all the devices and/or components on-board.

Whenever handling an ETX-A61 module, ground yourself through an anti-static wrist strap. Placement of the board on an anti-static surface is also highly recommended.

# 1.6 RoHS compliance

The ETX-A61 module is designed using RoHS compliant components and is manufactured on a lead-free production line. It is therefore fully RoHS compliant.

# 1.7 Terminology and definitions

| ACPI     | Advanced Configuration and Power Interface, an open industrial standard for the board's devices configuration and power management                                                                                       |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AHCI     | Advanced Host Controller Interface, a standard which defines the operations modes of SATA interface                                                                                                                      |

| API      | Application Program Interface, a set of commands and functions that can be used by programmers for writing software for specific Operating Systems                                                                       |

| BIOS     | Basic Input / Output System, the Firmware Interface that initializes the board before the OS starts loading                                                                                                              |

| CRT      | Cathode Ray Tube. Initially used to indicate a type of monitor, this acronym has been used over time to indicate the analog video interface used to drive them.                                                          |

| DDC      | Display Data Channel, a kind of I2C interface for digital communication between displays and graphics processing units (GPU)                                                                                             |

| DDR      | Double Data Rate, a typology of memory devices which transfer data both on the rising and on the falling edge of the clock                                                                                               |

| DDR3     | DDR, 3rd generation                                                                                                                                                                                                      |

| DP       | Display Port, a type of digital video display interface                                                                                                                                                                  |

| DVI      | Digital Visual interface, a type of digital video display interface                                                                                                                                                      |

| eDP      | embedded Display Port, a type of digital video display interface developed especially for internal connections between boards and digital displays                                                                       |

| EHCI     | Enhanced Host Controller interface, a high-speed controller for USB ports, able to support USB2.0 standard                                                                                                               |

| GbE      | Gigabit Ethernet                                                                                                                                                                                                         |

| Gbps     | Gigabits per second                                                                                                                                                                                                      |

| GND      | Ground                                                                                                                                                                                                                   |

| GPI/O    | General purpose Input/Output                                                                                                                                                                                             |

| HD Audio | High Definition Audio, most recent standard for hardware codecs developed by Intel® in 2004 for higher audio quality                                                                                                     |

| I2C Bus  | Inter-Integrated Circuit Bus, a simple serial bus consisting only of data and clock line, with multi-master capability                                                                                                   |

| ISA Bus  | Industry Standard Architecture Bus, an old parallel bus for the connection of expansion boards.                                                                                                                          |

| LPC Bus  | Low Pin Count Bus, a low speed interface based on a very restricted number of signals, deemed to management of legacy peripherals                                                                                        |

| LVDS     | Low Voltage Differential Signaling, a standard for transferring data at very high speed using inexpensive twisted pairs copper cables, usually used for video applications                                               |

| Mbps     | Megabits per second                                                                                                                                                                                                      |

| MMC/eMMC | MultiMedia Card / embedded MMC, a type of memory card, having the same interface as the SD card. The eMMC is the embedded version of the MMC. They are devices that incorporate the flash memories on a single BGA chip. |

| N.A.     | Not Applicable                                                                                                                                                                                                           |

|          |                                                                                                                                                                                                                          |

| N.C.   | Not Connected                                                                                                                                                             |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OpenGL | Open Graphics Library, an Open Source API dedicated to 2D and 3D graphics                                                                                                 |

| OS     | Operating System                                                                                                                                                          |

| PCI    | Peripheral Component Interconnect, a parallel bus working at 33MHz for the connection of external expansion board                                                         |

| PCI-e  | Peripheral Component Interconnect Express                                                                                                                                 |

| PSU    | Power Supply Unit                                                                                                                                                         |

| PWM    | Pulse Width Modulation                                                                                                                                                    |

| PWR    | Power                                                                                                                                                                     |

| PXE    | Preboot Execution Environment, a way to perform the boot from the network ignoring local data storage devices and/or the installed OS                                     |

| SATA   | Serial Advance Technology Attachment, a differential half duplex serial interface for Hard Disks                                                                          |

| SM Bus | System Management Bus, a subset of the I2C bus dedicated to communication with devices for system management, like smart batteries and other power supply-related devices |

| TBM    | To be measured                                                                                                                                                            |

| TMDS   | Transition-Minimized Differential Signaling, a method for transmitting high speed serial data, normally used on DVI and HDMI interfaces                                   |

| TTL    | Transistor-transistor Logic                                                                                                                                               |

| UEFI   | Unified Extensible Firmware Interface, a specification defining the interface between the OS and the board's firmware. It is meant to replace the original BIOS interface |

| USB    | Universal Serial Bus                                                                                                                                                      |

| V_REF  | Voltage reference Pin                                                                                                                                                     |

| VGA    | Video Graphics Array. An analog computer display standard, commonly referred to also as CRT.                                                                              |

|        |                                                                                                                                                                           |

# 1.8 Reference specifications

Here below it is a list of applicable industry specifications and reference documents.

| Reference                           | Link                                                                                                                       |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| ACPI                                | http://www.acpi.info                                                                                                       |

| AHCI                                | http://www.intel.com/content/www/us/en/io/serial-ata/ahci.html                                                             |

| DDC                                 | http://www.vesa.org                                                                                                        |

| ETX                                 | http://www.etx-ig.org/specs/specs.php                                                                                      |

| Gigabit Ethernet                    | http://standards.ieee.org/about/get/802/802.3.html                                                                         |

| HD Audio                            | http://www.intel.com/content/dam/www/public/us/en/documents/product-specifications/high-definition-audio-specification.pdf |

| I2C                                 | http://www.nxp.com/documents/other/UM10204_v5.pdf                                                                          |

| LPC Bus                             | http://www.intel.com/design/chipsets/industry/lpc.htm                                                                      |

| LVDS                                | http://www.ti.com/ww/en/analog/interface/lvds.shtml<br>http://www.ti.com/lit/ml/snla187.snla187.pdf                        |

| MMC/eMMC                            | http://www.jedec.org/committees/jc-649                                                                                     |

| OpenGL                              | http://www.opengl.org                                                                                                      |

| PCI                                 | https://www.pcisig.com/specifications/conventional                                                                         |

| PCI Express                         | http://www.pcisig.com/specifications/pciexpress                                                                            |

| SATA                                | https://www.sata-io.org                                                                                                    |

| SM Bus                              | http://www.smbus.org/specs                                                                                                 |

| UEFI                                | http://www.uefi.org                                                                                                        |

| USB 2.0                             | http://www.usb.org/developers/docs/usb_20_070113.zip                                                                       |

| Intel <sup>®</sup> Bay trail family | http://ark.intel.com/products/codename/55844/Bay-Trail#@Embedded                                                           |

# Chapter 2. OVERVIEW

- Introduction

- Technical Specifications

- Electrical Specifications

- Mechanical Specifications

- Block Diagram

# 2.1 Introduction

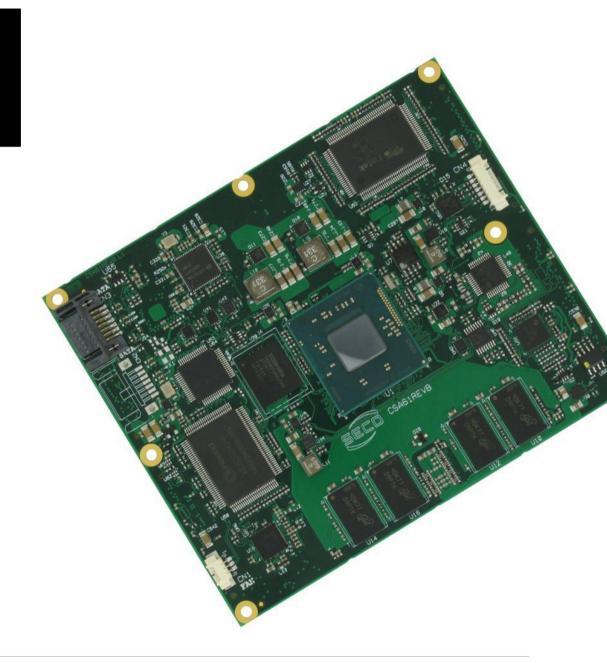

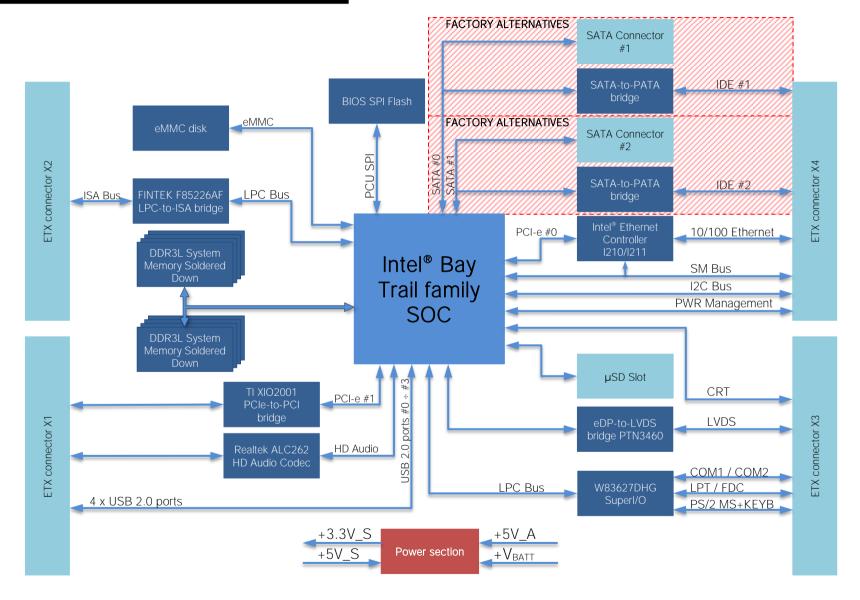

The ETX-A61 is a ETX<sup>®</sup> 3.0 compliant module, based on the Intel<sup>®</sup> family of System-on-Chips (SOCs) formerly coded as Bay Trail, a series of Single/ Dual / Quad Core SOCs with 64-bit instruction set. These SOCs embed all the features usually obtained by combination of CPU + platform Controller hubs, all in one single IC, which allows, therefore, the system minimisation and performance optimisation. A complete list of SOCs available is detailed in the next subchapter.

All the supported SOCs offer a 64-bit Instruction set, and provide direct access to the memory. Frequencies up to 1333MHz are supported, with a maximum capacity up to 8GB. Please notice that total amount of memory available is OS dependant, and depends also on the SOC.

All SOCs integrate an Intel<sup>®</sup> HD Graphics 4000 Series Controller, which offer high graphical performances, with support for Microsoft<sup>®</sup> DirectX11, OpenGL 3.0, OpenCL 1.2, OpenGL ES 2.0 and HW acceleration for video decoding of H.264, MPEG2, MVG, VC-1, VP8 and MJPEG video standards (for H.264, MPEG2 and MVG also HW encoding is offered). This embedded GPU is able to drive two independent displays; this can be obtained by exploiting both the native CRT (VGA) interface and the LVDS interface, which is realised through an eDP-to-LVDS bridge placed on one of the native Digital Display Interfaces available on the SOC.

For mass storage, on board it is possible to mount an optional eMMC disk. Furthermore, it is possible to connect external Hard Disk Drives by using the two native SATA channels of the SOC. ETX<sup>®</sup> specifications foresee the possibilities of having Parallel ATA interface on connector X4 and/or additional SATA connectors on top of the board. For this reason, since SATA channels available are only two, it is possible (as a factory option) to mount onboard one or two SATA-to-PATA bridges. Depending on the configuration purchased, therefore, it will be possible to have modules with two SATA connectors on top, **or** with two PATA interface on X4 and one SATA connector on top of the module.

The native HD Audio interface is connected to a Realtek ALC262 HD Audio Codec, so that it is possible to have analog audio channels (Stereo Output, Stereo auxiliary input and microphone input) on ETX connector X1.

Four USB 2.0 ports are supported directly by the SOC, ad are carried out directly on connector X1.

To complete the functionalities of the module, and make it compliant to ETX specifications, there are onboard a Gigabit Ethernet Controller (Intel<sup>®</sup> I210/I2111), which makes available the 10/100Mbps Ethernet interface, and a PCI-e-to-PCI bridge, to implement the PCI bus. Both these devices are managed by using two of the PCI-express ports #0 and #1, respectively.

Furthermore, on the LPC bus, are placed a LPC-to-ISA bridge, used to implement the ISA bus which characterize the ETX modules, and a Nuvoton SUperI/O, which makes available two full-modem serial ports, a parallel port shared with Floppy Disk interface, and PS/2 interface for Mouse and Keyboard.

The functionalities of this module are completed by the Real Time Clock, SM Bus, I2C Bus and the Watchdog. Please refer to following chapter for a complete list of all peripherals integrated and characteristics.

The module has a very rugged design, since it is based on soldered down DDR3L memories, ceramic capacitors only and high quality AEC-Q200 grade-1 inductors. The possibility of having an embedded storage device, the eMMC, makes this module particularly suited for applications where vibrations can represent a problem that must be faced.

The product is ETX<sup>®</sup> Rel.3.0 standard compliant, an industry standard defined specifically for COMs (computer on modules) which require ensuring support for legacy peripherals (like those requiring ISA bus, PCI bus and/or PS/2 interface). Its definition provides the ability to make a smooth transition from legacy parallel interfaces to the newest technologies based on serial buses available.

## 2.2 Technical Specifications

#### SOC

Intel<sup>®</sup> Atom<sup>™</sup> E3845, Quad Core @1.91GHz, 2MB Cache, 10W TDP Intel<sup>®</sup> Atom<sup>™</sup> E3827, Dual Core @1.75GHz, 1MB Cache, 8W TDP Intel<sup>®</sup> Atom<sup>™</sup> E3826, Dual Core @1.46GHz, 1MB Cache, 7W TDP Intel<sup>®</sup> Atom<sup>™</sup> E3825, Dual Core @1.33GHz, 1MB Cache, 6W TDP Intel<sup>®</sup> Atom<sup>™</sup> E3815, Single Core @1.46GHz, 512KB Cache, 5W TDP Intel<sup>®</sup> Celeron<sup>®</sup> J1900, Quad Core @2.0GHz, 2MB Cache, 10W TDP Intel<sup>®</sup> Celeron<sup>®</sup> N2930, Quad Core @1.83GHz, 2MB Cache, 7.5W TDP Intel<sup>®</sup> Celeron<sup>®</sup> N2807, Dual Core @1.58GHz, 1MB Cache, 4.3W TDP

#### Memory

Soldered down DDR3L memory E3845, E3827, J1900, N2930: up to 8GB Dual-Channel DDR3L 1333MHz E3826: up to 8GB Dual-Channel DDR3L 1066MHz N2807: up to 4GB Single-Channel DDR3L 1333MHz E3825, E3815: up to 4GB Single-Channel DDR3L 1066MHz

#### Graphics

Integrated Intel<sup>®</sup> HD Graphics 4000 series controller Dual independent display support HW decoding of H.264, MPEG2, MVC, VC1, VP8, MJPEG formats HW encoding of H.264, MPEG2 and MVC formats

#### Video Interfaces

VGA standard analog video interface 18/24 bit single/dual channel LVDS interface (VESA and JEIDA color mapping compatible)

#### Video Resolutions

CRT Interface: LVDS interface: up to 2560 x 1600 @ 60Hz Up to 1920 x 1200 @ 60Hz

#### Mass Storage

Optional eMMC disk soldered on board 2 x external S-ATA or 2 x P-ATA or 1x P-ATA + 1 x S-ATA channels (factory options) µSD Card Slot

#### USB

4 x USB 2.0 Host ports

#### Networking

Gigabit Ethernet controller, makes available a 10/100Mbps Ethernet interface

#### Audio

HD Audio codec, Realtek ALC262

#### Serial Ports

2 x Serial ports (TX/RX/RTS/CTS signals, TTL interface)

#### Other Interfaces

PCI Bus rel. 2.3 compliant, realised using a PCI-e to PCI bridge ISA Bus, realised using a LPC to ISA bridge LPT interface shared with Floppy Disk Drive interface PS/2 mouse and keyboard interface I2C Bus SM bus Watch Dog timer Power Management Signals Power supply voltage:  $+5V_{DC} \pm 5\%$  and  $+5V_{SB}$  (optional)

Operating temperature: 0°C ÷ +60°C (commercial version) \*\*

Dimensions: 114 x 95 mm (4.49" x 3.74")

\*\* Temperatures indicated are the minimum and maximum temperature that the heatspreader / heatsink can reach in any of its parts. This means that it is customer's responsibility to use any passive cooling solution along with an application-dependent cooling system, capable to ensure that the heatspreader / heatsink temperature remains in the range above indicated. Please also check paragraph 5.1

# 2.3 Electrical Specifications

According to  $ETX^{\otimes}$  specifications, the ETX-A61 board needs to be supplied only with an external  $+5V_{DC} \pm 5\%$  voltage ( $+5V_S$ ).

5 Volts standby voltage needs to be supplied for working in ATX mode.

For Real Time Clock working and CMOS memory data retention, it is also needed a backup battery voltage. It must be provided using pin 8 (BATT) of connector X4 (CN7).

All these voltages are supplied directly through ETX Connectors X1 (CN6), X2 (CN5), X3 (CN8) and X4 (CN7).

All remaining voltages needed for board's working are generated internally from +5V\_S power rail.

According to ETX<sup>®</sup> specifications, the +3.3V\_S voltage present on connector X1 pins 12, 16 and 24 is generated internally; therefore, it must be considered as a power output for devices on the carrier board that need this voltage. According to ETX<sup>®</sup> specifications, maximum external load admitted on +3.3V\_S power rail is 500mA.

Since +3.3V\_S is generated internally on ETX-A61 module, do not connect +3.3V\_S pins to external 3.3V power supply units.

## 2.3.1 Power Rails meanings

In all the tables contained in this manual, Power rails are named with the following meaning:

\_S: Switched voltages, i.e. power rails that are active only when the board is in ACPI's S0 (Working) state. Examples: +3.3V\_S, +5V\_S.

\_A: Always-on voltages, i.e. power rails that are active both in ACPI's S0 (Working), S3 (Standby) and S5 (Soft Off) state. Examples: +5V\_A, +3.3V\_A.

\_U: unswitched ACPI S3 voltages, i.e. power rails that are active both in ACPI's S0 (Working) and S3 (Standby) state. Examples: +1.5V\_U.

## 2.3.2 Power Consumption

TBM

# 2.4 Mechanical Specifications

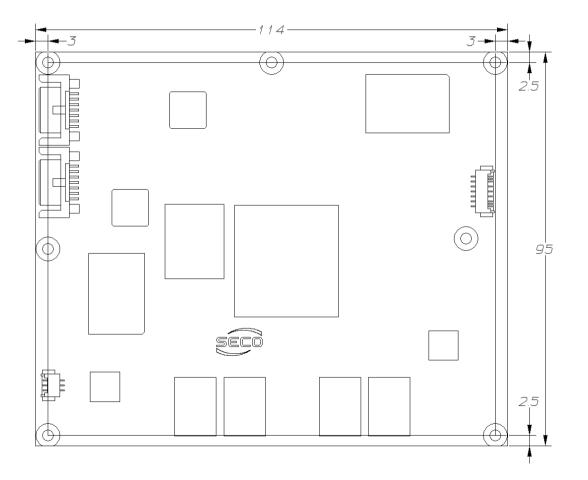

The ETX-A61 is an ETX<sup>®</sup> 3.0 compliant module; therefore its dimensions are 114 mm x 95 mm (4.49" x 3.74").

Printed circuit of the board is made of ten layers, some of them are ground planes, for disturbance rejection.

The ETX plugs used will allow a clearance under the module of about 3mm. Since there are components on the bottom of the module, it is necessary to avoid placing any component on the carrier board in the area under the ETX<sup>®</sup> module.

# 2.5 Block Diagram

SECO

# Chapter 3. CONNECTORS

- Introduction

- Connectors description

# 3.1 Introduction

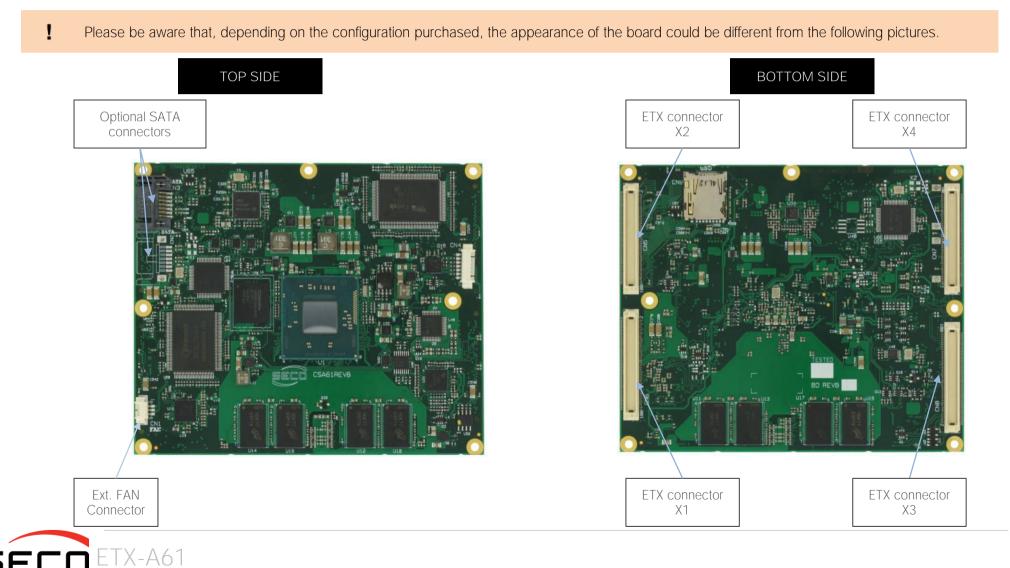

According to ETX<sup>®</sup> specifications, all interfaces to the board are available through two 220 pin connectors, for a total of 440 pin. Simplifying the terminology in this documentation, the primary connector is called A-B and the secondary C-D, since each one consists of two rows.

In addition, a Fan connector has been placed on one side of the board, in order to allow an easier connection of active heatsinks to the module.

ETX-A61 User Manual - Rev. First Edition: 1.0 - Last Edition: 1.2 - Author: S.B. - Reviewed by G.G. Copyright © 2017 SECO S.r.I.

# 3.2 Connectors description

### 3.2.1 FAN Connector

| FAN Connector - CN3 | Depending on the usage model of ETX-A61 module, for critical applications/environments on the module itself it is available a 3-<br>pin dedicated connector for an external +5V <sub>DC</sub> FAN. |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Signal          | FAN Connector is a 3-pin single line SMT connector, type MOLEX 53261-0319 or equivalent, with pinout shown in                                                                                      |

| 1 GND               | the table on the left.                                                                                                                                                                             |

| 2 FAN_POWER         | Mating connector: MOLEX 51021-0300 receptacle with MOLEX 50079-8000 female crimp terminals.                                                                                                        |

| 3 FAN_TACHO_IN      | Please be aware that the use of an external fan depends strongly on customer's application/installation.                                                                                           |

|                     | Please refer to chapter 5.1 for considerations about thermal dissipation.                                                                                                                          |

FAN\_POWER: +5V\_S derived power rail for FAN, managed by the embedded microcontroller via PWM signal.

FAN\_TACHO\_IN: tachometric input from the fan to the embedded microcontroller, +3.3V\_S electrical level signal.

### 3.2.2 SATA connectors

|     | Optional SATA #0<br>Connector - CN3 | Optional SATA #1<br>Connector - CN2 |           |  |

|-----|-------------------------------------|-------------------------------------|-----------|--|

| Pin | Signal                              | Pin                                 | Signal    |  |

| 1   | GND                                 | 1                                   | GND       |  |

| 2   | SATA0_TX+                           | 2                                   | SATA1_TX+ |  |

| 3   | SATA0_TX-                           | 3                                   | SATA1_TX- |  |

| 4   | GND                                 | 4                                   | GND       |  |

| 5   | SATAO_RX-                           | 5                                   | SATA1_RX- |  |

| 6   | SATA0_RX+                           | 6                                   | SATA1_RX+ |  |

| 7   | GND                                 | 7                                   | GND       |  |

The SOCs used on ETX-A61 module have an integrated S-ATA controller, which offers a SATA II, 3.0 Gps interface, capable to use up to two independent devices. These two channels can be carried out on externally on connectors CN2 and CN3, which are standard right-angle S-ATA connectors, to be used for connection of external Mass Storage Devices.

Both these connectors are optional, since the two SATA channels can be used (as a factory option) to drive a SATA-to-PATA bridge, which will make available the primary and/or the secondary IDE Channel on ETX connector X4 (CN7).

Please also check par. 3.2.5.10.

|       | -                   |

|-------|---------------------|

| PIN 1 | / <sup>-PIN 7</sup> |

|       | Ĺ                   |

|       | TR_                 |

1

## 3.2.3 µSD Card Slot

The SOCs used on ETX-A61 module offer a SD 3.0 compliant interface, that can be used to implement another mass storages media other than the optional internal eMMC and the two SATA/PATA interfaces.

This SD interface is carried to a standard  $\mu$ SD card slot, soldered on top side of the module, push-push type.

### 3.2.4 ETX<sup>®</sup> Module connectors

ETX-A61

For the connection of ETX<sup>®</sup> CPU modules, on board there are 4 connectors, type HIROSE FX8-100P-SV(92) (100 pin, ultra slim, 0.6mm pitch, h=2.45mm), according to the ETX<sup>®</sup> specifications.

The pinout of the module is compliant to ETX<sup>®</sup> specifications. Not all the signals contemplated in ETX<sup>®</sup> standard are implemented on the double connector, due to the functionalities really implemented on ETX-A61 board. Therefore, please

refer to the following table for a list of effective signals reported on the connector. For accurate signals description, please consult the following paragraphs.

#### 3.2.4.1 X1 CONNECTOR: PCI Bus, USB, Audio

|              |      |          | ETX <sup>®</sup> Connec | ctor X1 | - CN6    |      |              |

|--------------|------|----------|-------------------------|---------|----------|------|--------------|

| SIGNAL GROUP | Туре | Pin name | Pin nr.                 | Pin nr. | Pin name | Туре | SIGNAL GROUP |

|              | PWR  | GND      | 1                       | 2       | GND      | PWR  |              |

| PCI          | 0    | PCICLK3  | 3                       | 4       | PCICLK4  | 0    | PCI          |

|              | PWR  | GND      | 5                       | 6       | GND      | PWR  |              |

| PCI          | 0    | PCICLK1  | 7                       | 8       | PCICLK2  | 0    | PCI          |

| PCI          | I    | REQ3#    | 9                       | 10      | GNT3#    | 0    | PCI          |

| PCI          | 0    | GNT2#    | 11                      | 12      | +3.3V_S  | PWR  |              |

| PCI          | I    | REQ2#    | 13                      | 14      | GNT1#    | 0    | PCI          |

| PCI          | I    | REQ1#    | 15                      | 16      | +3.3V_S  | PWR  |              |

| PCI          | 0    | GNT0#    | 17                      | 18      | N.C.     | N.A. |              |

|              | PWR  | +5V_S    | 19                      | 20      | +5V_S    | PWR  |              |

| MISC         | I    | SERIRQ   | 21                      | 22      | REQ0#    |      | PCI          |

| PCI          | I/O  | ADO      | 23                      | 24      | +3.3V_S  | PWR  |              |

| PCI          | I/O  | AD1      | 25                      | 26      | AD2      | I/O  | PCI          |

| PCI          | I/O  | AD4      | 27                      | 28      | AD3      | I/O  | PCI          |

| PCI          | I/O  | AD6      | 29                      | 30      | AD5      | I/O  | PCI          |

| PCI          | I/O  | CBEO#    | 31                      | 32      | AD7      | I/O  | PCI          |

| PCI          | I/O  | AD8      | 33                      | 34      | AD9      | I/O  | PCI          |

|              | PWR  | GND      | 35                      | 36      | GND      | PWR  |              |

| PCI          | I/O  | AD10     | 37                      | 38      | AUXAL    | I    | AUDIO        |

| PCI          | I/O  | AD11     | 39                      | 40      | MIC      | 1    | AUDIO        |

ETX-A61 User Manual - Rev. First Edition: 1.0 - Last Edition: 1.2 - Author: S.B. - Reviewed by G.G. Copyright © 2017 SECO S.r.l.

| PCI | I/O | AD12    | 41 | 42  | AUXAR   | 1    | AUDIO |

|-----|-----|---------|----|-----|---------|------|-------|

| PCI | I/O | AD13    | 43 | 44  | N.C.    | PWR  | AUDIO |

| PCI | I/O | AD14    | 45 | 46  | SNDL    | 0    | AUDIO |

| PCI | I/O | AD15    | 47 | 48  | ASGND   | PWR  | AUDIO |

| PCI | I/O | CBE1#   | 49 | 50  | SNDR    | 0    | AUDIO |

|     | PWR | +5V_S   | 51 | 52  | +5V_S   | PWR  |       |

| PCI | I/O | PAR     | 53 | 54  | SERR#   | I/O  | PCI   |

| PCI | I/O | GPERR#  | 55 | 56  | N.C.    | N.A. |       |

| PCI | I   | PME#    | 57 | 58  | USB2-   | I/O  | USB   |

| PCI | I/O | LOCK#   | 59 | 60  | DEVSEL# | I/O  | PCI   |

| PCI | I/O | TRDY#   | 61 | 62  | USB3-   | I/O  | USB   |

| PCI | I/O | IRDY#   | 63 | 64  | STOP#   | I/O  | PCI   |

| PCI | I/O | FRAME#  | 65 | 66  | USB2+   | I/O  | USB   |

|     | PWR | GND     | 67 | 68  | GND     | PWR  |       |

| PCI | I/O | AD16    | 69 | 70  | CBE2#   | I/O  | PCI   |

| PCI | I/O | AD17    | 71 | 72  | USB3+   | I/O  | USB   |

| PCI | I/O | AD19    | 73 | 74  | AD18    | I/O  | PCI   |

| PCI | I/O | AD20    | 75 | 76  | USB0-   | I/O  | USB   |

| PCI | I/O | AD22    | 77 | 78  | AD21    | I/O  | PCI   |

| PCI | I/O | AD23    | 79 | 80  | USB1-   | I/O  | USB   |

| PCI | I/O | AD24    | 81 | 82  | CBE3#   | I/O  | PCI   |

|     | PWR | +5V_S   | 83 | 84  | +5V_S   | PWR  |       |

| PCI | I/O | AD25    | 85 | 86  | AD26    | I/O  | PCI   |

| PCI | I/O | AD28    | 87 | 88  | USB0+   | I/O  | USB   |

| PCI | I/O | AD27    | 89 | 90  | AD29    | I/O  | PCI   |

| PCI | I/O | AD30    | 91 | 92  | USB1+   | I/O  | USB   |

| PCI | О   | PCIRST# | 93 | 94  | AD31    | I/O  | PCI   |

| PCI | I   | INTC#   | 95 | 96  | INTD#   | I    | PCI   |

| PCI | I   | INTA#   | 97 | 98  | INTB#   | I    | PCI   |

|     | PWR | GND     | 99 | 100 | GND     | PWR  |       |

|     |     |         |    |     |         |      |       |

**SECO** ETX-A61 ETX-A61 User Manual - Rev. First Edition: 1.0 - Last Edition: 1.2 - Author: S.B. - Reviewed by G.G. Copyright © 2017 SECO S.r.l.

### 3.2.4.2 X2 CONNECTOR: ISA Bus

|              |      |          | ETX <sup>®</sup> Connec | ctor X2 | - CN5    |      |              |

|--------------|------|----------|-------------------------|---------|----------|------|--------------|

| SIGNAL GROUP | Туре | Pin name | Pin nr.                 | Pin nr. | Pin name | Туре | SIGNAL GROUP |

|              | PWR  | GND      | 1                       | 2       | GND      | PWR  |              |

| ISA          | I/O  | SD14     | 3                       | 4       | SD15     | I/O  | ISA          |

| ISA          | I/O  | SD13     | 5                       | 6       | MASTER#  |      | ISA          |

| ISA          | I/O  | SD12     | 7                       | 8       | DREQ7    | I    | ISA          |

| ISA          | I/O  | SD11     | 9                       | 10      | DACK7#   | 0    | ISA          |

| ISA          | I/O  | SD10     | 11                      | 12      | DREQ6    | 1    | ISA          |

| ISA          | I/O  | SD9      | 13                      | 14      | DACK6#   | 0    | ISA          |

| ISA          | I/O  | SD8      | 15                      | 16      | DREQ5    | 1    | ISA          |

| ISA          | I/O  | MEMW#    | 17                      | 18      | DACK5#   | 0    | ISA          |

| ISA          | I/O  | MEMR#    | 19                      | 20      | DREQO    | I    | ISA          |

| ISA          | I/O  | LA17     | 21                      | 22      | DACK0#   | 0    | ISA          |

| ISA          | I/O  | LA18     | 23                      | 24      | IRQ14    | I    | ISA          |

| ISA          | I/O  | LA19     | 25                      | 26      | IRQ15    | I    | ISA          |

| ISA          | I/O  | LA20     | 27                      | 28      | IRQ12    | I    | ISA          |

| ISA          | I/O  | LA21     | 29                      | 30      | IRQ11    | I    | ISA          |

| ISA          | I/O  | LA22     | 31                      | 32      | IRQ10    | I    | ISA          |

| ISA          | I/O  | LA23     | 33                      | 34      | IO16#    | I/O  | ISA          |

|              | PWR  | GND      | 35                      | 36      | GND      | PWR  |              |

| ISA          | I/O  | SBHE#    | 37                      | 38      | M16#     | I/O  | ISA          |

| ISA          | I/O  | SAO      | 39                      | 40      | OSC      | 0    | ISA          |

| ISA          | I/O  | SA1      | 41                      | 42      | BALE     | I/O  | ISA          |

| ISA          | I/O  | SA2      | 43                      | 44      | TC       | 0    | ISA          |

| ISA          | I/O  | SA3      | 45                      | 46      | DACK2#   | 0    | ISA          |

| ISA          | I/O  | SA4      | 47                      | 48      | IRQ3     | I    | ISA          |

| ISA          | I/O  | SA5      | 49                      | 50      | IRQ4     | I    | ISA          |

|              | PWR  | +5V_S    | 51                      | 52      | +5V_S    | PWR  |              |

**SECO** ETX-A61 ETX-A61 User Manual - Rev. First Edition: 1.0 - Last Edition: 1.2 - Author: S.B. - Reviewed by G.G. Copyright © 2017 SECO S.r.I.

| ISA | I/O | SA6     | 53 | 54  | IRQ5   |     | ISA |

|-----|-----|---------|----|-----|--------|-----|-----|

| ISA | I/O | SA7     | 55 | 56  | IRQ6   |     | ISA |

| ISA | I/O | SA8     | 57 | 58  | IRQ7   |     | ISA |

| ISA | I/O | SA9     | 59 | 60  | SYSCLK | 0   | ISA |

| ISA | I/O | SA10    | 61 | 62  | REFSH# | 0   | ISA |

| ISA | I/O | SA11    | 63 | 64  | DREQ1  | 1   | ISA |

| ISA | I/O | SA12    | 65 | 66  | DACK1# | 0   | ISA |

|     | PWR | GND     | 67 | 68  | GND    | PWR |     |

| ISA | I/O | SA13    | 69 | 70  | DREQ3  |     | ISA |

| ISA | I/O | SA14    | 71 | 72  | DACK3# | 0   | ISA |

| ISA | I/O | SA15    | 73 | 74  | IOR#   | I/O | ISA |

| ISA | I/O | SA16    | 75 | 76  | IOW#   | I/O | ISA |

| ISA | I/O | SA18    | 77 | 78  | SA17   | I/O | ISA |

| ISA | I/O | SA19    | 79 | 80  | SMEMR# | 0   | ISA |

| ISA | I/O | IOCHRDY | 81 | 82  | AEN    | 0   | ISA |

|     | PWR | +5V_S   | 83 | 84  | +5V_S  | PWR |     |

| ISA | I/O | SD0     | 85 | 86  | SMEMW# | 0   | ISA |

| ISA | I/O | SD2     | 87 | 88  | SD1    | I/O | ISA |

| ISA | I/O | SD3     | 89 | 90  | NOWS#  | 1   | ISA |

| ISA | L   | DREQ2   | 91 | 92  | SD4    | I/O | ISA |

| ISA | I/O | SD5     | 93 | 94  | IRQ9   |     | ISA |

| ISA | I/O | SD6     | 95 | 96  | SD7    | I/O | ISA |

| ISA | I   | IOCHK#  | 97 | 98  | RSTDRV | 0   | ISA |

|     | PWR | GND     | 99 | 100 | GND    | PWR |     |

|     |     |         |    |     |        |     |     |

| ETX <sup>®</sup> Connector X3 - CN8 |      |             |         |         |               |      |              |  |  |

|-------------------------------------|------|-------------|---------|---------|---------------|------|--------------|--|--|

| SIGNAL GROUP                        | Туре | Pin name    | Pin nr. | Pin nr. | Pin name      | Туре | SIGNAL GROUP |  |  |

|                                     | PWR  | GND         | 1       | 2       | GND           | PWR  |              |  |  |

| VGA                                 | 0    | R           | 3       | 4       | В             | 0    | VGA          |  |  |

| VGA                                 | 0    | HSY         | 5       | 6       | G             | 0    | VGA          |  |  |

| VGA                                 | 0    | VSY         | 7       | 8       | DDCK          | 0    | VGA          |  |  |

|                                     | N.A. | N.C.        | 9       | 10      | DDDA          | I/O  | VGA          |  |  |

| LVDS                                | 0    | LVDS_CLK_B- | 11      | 12      | LVDS_B3-      | 0    | LVDS         |  |  |

| LVDS                                | 0    | LVDS_CLK_B+ | 13      | 14      | LVDS_B3+      | 0    | LVDS         |  |  |

|                                     | PWR  | GND         | 15      | 16      | GND           | PWR  |              |  |  |

| LVDS                                | 0    | LVDS_B1+    | 17      | 18      | LVDS_B2+      | 0    | LVDS         |  |  |

| LVDS                                | 0    | LVDS_B1-    | 19      | 20      | LVDS_B2-      | 0    | LVDS         |  |  |

|                                     | PWR  | GND         | 21      | 22      | GND           | PWR  |              |  |  |

| LVDS                                | 0    | LVDS_A3-    | 23      | 24      | LVDS_B0+      | 0    | LVDS         |  |  |

| LVDS                                | 0    | LVDS_A3+    | 25      | 26      | LVDS_B0-      | 0    | LVDS         |  |  |

|                                     | PWR  | GND         | 27      | 28      | GND           | PWR  |              |  |  |

| LVDS                                | 0    | LVDS_A2-    | 29      | 30      | LVDS_CLK_A+   | 0    | LVDS         |  |  |

| LVDS                                | 0    | LVDS_A2+    | 31      | 32      | LVDS_CLK_A-   | 0    | LVDS         |  |  |

|                                     | PWR  | GND         | 33      | 34      | GND           | PWR  |              |  |  |

| LVDS                                | 0    | LVDS_A0+    | 35      | 36      | LVDS_A1+      | 0    | LVDS         |  |  |

| LVDS                                | 0    | LVDS_A0-    | 37      | 38      | LVDS_A1-      | 0    | LVDS         |  |  |

|                                     | PWR  | +5V_S       | 39      | 40      | +5V_S         | PWR  |              |  |  |

| LVDS                                | I/O  | JILI_DAT    | 41      | 42      | LVDS_BLT_CTRL | Ο    | LVDS         |  |  |

| LVDS                                | I/O  | JILI_CLK    | 43      | 44      | BLON#         | 0    | LVDS         |  |  |

| LVDS                                | 0    | BIASON      | 45      | 46      | DIGON         | Ο    | LVDS         |  |  |

|                                     | N.A. | N.C.        | 47      | 48      | N.C.          | N.A. |              |  |  |

|                                     | N.A. | N.C.        | 49      | 50      | N.C.          | N.A. |              |  |  |

| PARALLEL                            | I    | LPT/FLPY#   | 51      | 52      | N.C.          | N.A. |              |  |  |

### 3.2.4.3 X3 CONNECTOR: VGA, LVDS, COMs, LPT/FLOPPY, PS/2

**SECO** ETX-A61 ETX-A61 User Manual - Rev. First Edition: 1.0 - Last Edition: 1.2 - Author: S.B. - Reviewed by G.G. Copyright © 2017 SECO S.r.I.

|        | PWR  | +5V_S  | ! | 53 | 54  | GND            | PW  | PWR |          |

|--------|------|--------|---|----|-----|----------------|-----|-----|----------|

|        | O    | STB# / | ! | 55 | 56  | AFD# / DENSEL  | 0   | Ο   | PARALLEL |

|        | N.A. | N.C.   |   | 57 | 58  | PD7 /          | I/O |     | PARALLEL |

| SERIAL | I    | IRRX   |   | 59 | 60  | ERR# / HDSEL#  | 1   | 0   | PARALLEL |

| SERIAL | 0    | IRTX   |   | 61 | 62  | PD6 /          | I/O |     | PARALLEL |

| SERIAL | I    | RXD2   |   | 63 | 64  | INIT# / DIR#   | 0   | 0   | PARALLEL |

|        | PWR  | GND    |   | 65 | 66  | GND            | PW  | R   |          |

| SERIAL | 0    | RTS2#  |   | 67 | 68  | PD5 /          | I/O |     | PARALLEL |

| SERIAL | 0    | DTR2#  |   | 69 | 70  | SLIN# / STEP#  | 0   | 0   | PARALLEL |

| SERIAL | I    | DCD2#  |   | 71 | 72  | PD4 / DSKCHG # | I/O |     | PARALLEL |

| SERIAL | I    | DSR2#  |   | 73 | 74  | PD3 / RDATA#   | I/O | I   | PARALLEL |

| SERIAL | I    | CTS2#  |   | 75 | 76  | PD2 / WP#      | I/O |     | PARALLEL |

| SERIAL | 0    | TXD2#  |   | 77 | 78  | PD1 /TRK0#     | I/O | I   | PARALLEL |

| SERIAL | I    | RI2#   |   | 79 | 80  | PD0 / INDEX#   | I/O |     | PARALLEL |

|        | PWR  | GND    |   | 81 | 82  | GND            | PW  | R   |          |

| SERIAL | I    | RXD1   |   | 83 | 84  | ACK# / DRV#    | l.  | 0   | PARALLEL |

| SERIAL | 0    | RTS1#  |   | 85 | 86  | BUSY / MOT#    | I   | 0   | PARALLEL |

| SERIAL | 0    | DTR1#  |   | 87 | 88  | PE / WDATA #   | l.  | 0   | PARALLEL |

| SERIAL | I    | DCD1#  | : | 89 | 90  | SLCT / WGATE#  | I   | 0   | PARALLEL |

| SERIAL | L    | DSR1#  |   | 91 | 92  | MSCLK          | I/O | С   | PS/2     |

| SERIAL | I    | CTS1#  |   | 93 | 94  | MSDAT          | I/C | )   | PS/2     |

| SERIAL | 0    | TXD1   |   | 95 | 96  | KBCLK          | I/C | )   | PS/2     |

| SERIAL | I    | RI1#   |   | 97 | 98  | KBDAT          | I/C | )   | PS/2     |

|        | PWR  | GND    |   | 99 | 100 | GND            | PW  | R   |          |

|        |      |        |   |    |     |                |     |     |          |

| ETX <sup>®</sup> Connector X4 - CN7 |      |            |            |         |            |      |              |  |  |

|-------------------------------------|------|------------|------------|---------|------------|------|--------------|--|--|

| SIGNAL GROUP                        | Туре | Pin name   | Pin<br>nr. | Pin nr. | Pin name   | Туре | SIGNAL GROUP |  |  |

|                                     | PWR  | GND        | 1          | 2       | GND        | PWR  |              |  |  |

|                                     | PWR  | +5V_A      | 3          | 4       | PWGIN      | 1    | PWR_CTRL     |  |  |

| PWR_CTRL                            | 0    | PS_ON#     | 5          | 6       | SPEAKER    | 0    | MISC         |  |  |

| PWR_CTRL                            | I    | PWRBTN#    | 7          | 8       | BATT       | PWR  |              |  |  |

| MISC                                | I    | KBINH#     | 9          | 10      | LILED#     | 0    | ETHERNET     |  |  |

| PWR_MGMT                            | I    | RSMRST#    | 11         | 12      | ACTLED#    | 0    | ETHERNET     |  |  |

|                                     | N.A. | N.C.       | 13         | 14      | SPEEDLED#  | 0    | ETHERNET     |  |  |

|                                     | N.A. | N.C.       | 15         | 16      | I2CLK      | I/O  | MISC         |  |  |

|                                     | PWR  | +5V_S      | 17         | 18      | +5V_S      | PWR  |              |  |  |

| USB                                 | I    | OVCR#      | 19         | 20      | GPCS#      | 0    | MISC         |  |  |

| PWR_MGMT                            | I    | EXTSMI#    | 21         | 22      | I2DAT      | I/O  | MISC         |  |  |

| MISC                                | I/O  | SMBCLK     | 23         | 24      | SMBDATA    | I/O  | MISC         |  |  |

| IDE                                 | 0    | SIDE_CS3#  | 25         | 26      | SMBALRT#   | I    | PWR_MGMT     |  |  |

| IDE                                 | 0    | SIDE_CS1#  | 27         | 28      | N.C.       | N.A. |              |  |  |

| IDE                                 | I/O  | SIDE_A2    | 29         | 30      | PIDE_CS3#  | 0    | IDE          |  |  |

| IDE                                 | I/O  | SIDE_A0    | 31         | 32      | PIDE_CS1#  | 0    | IDE          |  |  |

|                                     | PWR  | GND        | 33         | 34      | GND        | PWR  |              |  |  |

|                                     | N.A. | N.C.       | 35         | 36      | PIDE_A2    | I/O  | IDE          |  |  |

| IDE                                 | I/O  | SIDE_A1    | 37         | 38      | PIDE_A0    | I/O  | IDE          |  |  |

| IDE                                 | I    | SIDE_INTRQ | 39         | 40      | PIDE_A1    | I/O  | IDE          |  |  |

| PWR_MGMT                            | I    | BATLOW#    | 41         | 42      | GPE1#      | I    | PWR_MGMT     |  |  |

| IDE                                 | 0    | SIDE_AK#   | 43         | 44      | PIDE_INTRQ | I.   | IDE          |  |  |

| IDE                                 | I    | SIDE_RDY   | 45         | 46      | PIDE_AK#   | 0    | IDE          |  |  |

| IDE                                 | 0    | SIDE_IOR#  | 47         | 48      | PIDE_RDY   | 1    | IDE          |  |  |

|                                     | PWR  | +5V_S      | 49         | 50      | +5V_S      | PWR  |              |  |  |

### 3.2.4.4 X4 CONNECTOR: IDE, ETHERNET, MISCELLANEOUS

**SECO** ETX-A61 ETX-A61 User Manual - Rev. First Edition: 1.0 - Last Edition: 1.2 - Author: S.B. - Reviewed by G.G. Copyright © 2017 SECO S.r.I.

| IDE      | 0   | SIDE_IOW# | 51 | 52  | PIDE_IOR# | 0    | IDE |

|----------|-----|-----------|----|-----|-----------|------|-----|

| IDE      | I   | SIDE_DRQ  | 53 | 54  | PIDE_IOW# | 0    | IDE |

| IDE      | I/O | SIDE_D15  | 55 | 56  | PIDE_DRQ  | I    | IDE |

| IDE      | I/O | SIDE_D0   | 57 | 58  | PIDE_D15  | I/O  | IDE |

| IDE      | I/O | SIDE_D14  | 59 | 60  | PIDE_D0   | I/O  | IDE |

| IDE      | I/O | SIDE_D1   | 61 | 62  | PIDE_D14  | I/O  | IDE |

| IDE      | I/O | SIDE_D13  | 63 | 64  | PIDE_D1   | I/O  | IDE |

|          | PWR | GND       | 65 | 66  | GND       | PWR  |     |

| IDE      | I/O | SIDE_D2   | 67 | 68  | PIDE_D13  | I/O  | IDE |

| IDE      | I/O | SIDE_D12  | 69 | 70  | PIDE_D2   | I/O  | IDE |

| IDE      | I/O | SIDE_D3   | 71 | 72  | PIDE_D12  | I/O  | IDE |

| IDE      | I/O | SIDE_D11  | 73 | 74  | PIDE_D3   | I/O  | IDE |

| IDE      | I/O | SIDE_D4   | 75 | 76  | PIDE_D11  | I/O  | IDE |

| IDE      | I/O | SIDE_D10  | 77 | 78  | PIDE_D4   | I/O  | IDE |

| IDE      | I/O | SIDE_D5   | 79 | 80  | PIDE_D10  | I/O  | IDE |

|          | PWR | +5V_S     | 81 | 82  | +5V_S     | PWR  |     |

| IDE      | I/O | SIDE_D9   | 83 | 84  | PIDE_D5   | I/O  | IDE |

| IDE      | I/O | SIDE_D6   | 85 | 86  | PIDE_D9   | I/O  | IDE |

| IDE      | I/O | SIDE_D8   | 87 | 88  | PIDE_D6   | I/O  | IDE |

| PWR_MGMT | I   | GPE2#     | 89 | 90  | N.C.      | N.A. |     |

| ETHERNET | I   | RXD-      | 91 | 92  | PIDE_D8   | I/O  | IDE |

| ETHERNET | I   | RXD+      | 93 | 94  | SIDE_D7   | I/O  | IDE |

| ETHERNET | О   | TXD-      | 95 | 96  | PIDE_D7   | I/O  | IDE |

| ETHERNET | 0   | TXD+      | 97 | 98  | HDRST#    | 0    | IDE |

|          | PWR | GND       | 99 | 100 | GND       | PWR  |     |

|          |     |           |    |     |           |      |     |

### 3.2.5 Signals description

## 3.2.5.1 PCI Signals (connector X1 - CN6)

Since the SOCs used on ETX-A61 module doesn't offer native support for PCI bus (which is required by ETX<sup>®</sup> specifications), this kind of interface is realised using a PCI-express to PCI bridge (Texas Instruments<sup>®</sup> XIO2001). This allows implementing a PCI bus compliant to PCI Local specifications rel. 2.3.

All signals are 3.3V voltage tolerant.

Here following the signals related to the PCI Bus.

PCICLK[1..4]: PCI clock outputs, for driving up to 4 external PCI slots or devices.

REQ[0..3]#: PCI Bus Request, +3.3V\_S active low inputs with 10kΩ pull-up resistor. Used by external bus mastering devices to request PCI bus ownership.

GNT[0..3]#: PCI Bus Grant, +3.3V\_S active low outputs. Used by the arbiter to grant the ownership of the bus.

AD[0..31]: PCI address and Data Bus lines, +3.3V\_S bidirectional signals.

CBE[0..3]#: PCI Bus command and byte enable, +3.3V\_S active low bidirectional signals. Multiplexed signals, used during the address phase and during the data phase of a transaction respectively to transfer a command and enable byte lanes.

PAR: PCI bus parity bit, +3.3V\_S bidirectional signal.

SERR#: System Error, +3.3V\_S active low bidirectional signals with  $10k\Omega$  pull-up resistor. Used to signals system errors

GPERR#: PCI bus Parity Error, +3.3V\_S active low bidirectional signals with  $10k\Omega$  pull-up resistor. Used to report data parity errors during PCI transactions.

PME#: Power Management Event, +3.3V\_A active low input signal with 10kΩ pull-up resistor. Used by external devices to request a change in the device or system power states.

LOCK#: Lock Resource, +3.3V\_S active low bidirectional signals with  $10k\Omega$  pull-up resistor. This signal is used to require exclusive use of the bus to complete an atomic operation that otherwise could require multiple transactions.

DEVSEL#: PCI Device Select, +3.3V\_S active low bidirectional signals with  $10k\Omega$  pull-up resistor. This signal is driven low by any device that, during a PCI transaction, has decoded its own address as the target of the transaction.

TRDY#: PCI Target Ready, +3.3V\_S active low bidirectional signals with 10k  $\Omega$  pull-up resistor. Used by the targeted device to signal that it is ready to complete the transaction.

IRDY#: PCI Initiator Ready, +3.3V\_S active low bidirectional signals with  $10k\Omega$  pull-up resistor. Used by the Bus Master to signal that it is ready to complete the transaction.

STOP#: PCI Stop, +3.3V\_S active low bidirectional signals with  $10k\Omega$  pull-up resistor. Used by the targeted device to request to the bus master to stop the current transaction.

FRAME#: PCI Cycle Frame indicator, +3.3V\_S active low bidirectional signals with  $10k\Omega$  pull-up resistor. This signal is used by the Bus Master to indicate the beginning of a transaction, and remains low (asserted) until the transaction is finished or in the final phase.

PCIRST#: PCI Reset, +3.3V\_S active low output with 10kΩ pull-up resistor. It is driven low during system reset to reset the whole PCI bus

INTA#, INTB#, INTC#, INTD#: PCI interrupt lines, +3.3V\_S active low inputs with 10k $\Omega$  pull-up resistor.

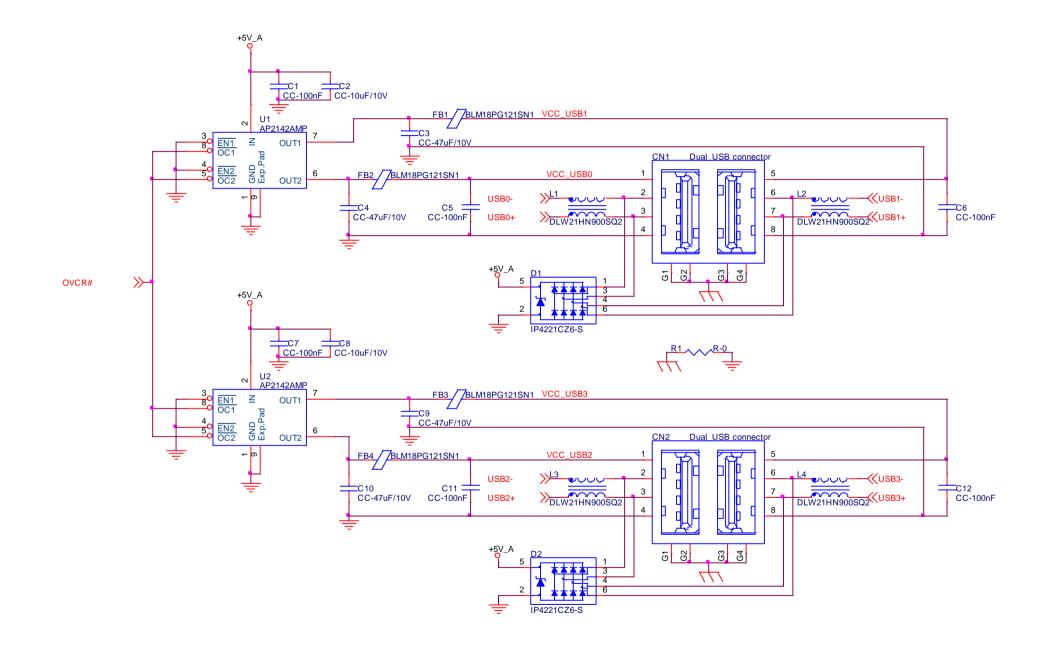

### 3.2.5.2 USB interface signals (connector X1 - CN6)

Intel<sup>®</sup> Bay Trail family of SOCs embeds one EHCl controller, which is able to manage up to four USB 1.x / 2.0 Host ports.

On ETX-A61 module, these four USB 2.0 ports are carried out directly on connector X1 (CN6). All of them are able to work in High Speed (HS), Full Speed (FS) and Low Speed (LS).

Via BIOS it is possible to enable or disable singularly each USB port.

Here following the signals related to USB interfaces.

USB0+/USB0-: Universal Serial Bus Port #0 bidirectional differential pair.

USB1+/USB1-: Universal Serial Bus Port #1 bidirectional differential pair.

USB2+/USB2-: Universal Serial Bus Port #2 bidirectional differential pair.

USB3+/USB3-: Universal Serial Bus Port #3 bidirectional differential pair.

OVCR#: USB Over Current Detect Input. Active Low Input signal, electrical level +3.3V\_A with 10kΩ pull-up resistor. This pin (available on connector X4 - CN7) has to be used for overcurrent detection of USB Ports of ETX-A61 module

Please notice that for correct management of Overcurrent signals, power distribution switches are needed on the carrier board.

For EMI/ESD protection, common mode chokes on USB data lines, and clamping diodes on USB data and voltage lines, are also needed.

The schematics in the following page show an example of implementation on the Carrier Board. In there, all USB ports #0, #1, #2 and #3 are carried out to standard USB 2.0 Type A receptacles.

All schematics (henceforth also referred to as material) contained in this manual are provided by SECO S.r.l. for the sole purpose of supporting the customers' internal development activities.

The schematics are provided "AS IS". SECO makes no representation regarding the suitability of this material for any purpose or activity and disclaims all warranties and conditions with regard to said material, including but not limited to, all expressed or implied warranties and conditions of merchantability, suitability for a specific purpose, title and non-infringement of any third party intellectual property rights.

The customer acknowledges and agrees to the conditions set forth that these schematics are provided only as an example and that he will conduct an independent analysis and exercise judgment in the use of any and all material. SECO declines all and any liability for use of this or any other material in the customers' product design

### 3.2.5.3 Audio interface signals (connector X1 - CN6)

The ETX-A61 module supports HD audio format, thanks to native support offered by the processor to this audio codec standard.

A Realtek ALC262 HD audio coded is embedded onboard. By using this codec, the ETX-A61 module is able to support the following audio signals.

SNDL/SNDR: Left and Right stereo output, ~1Vrms.

AUXAL/AUXAR: Left and Right auxiliary inputs, ~1Vrms

MIC: Microphone Input, ~1Vrms

ASGND: Analog ground reference. To be used on the carrier board for definition of an analog plane where tracing all audio signals.

### 3.2.5.4 ISA Signals (connector X2 - CN5)

Since the SOCs used on ETX-A61 module doesn't offer native support for ISA bus (which is required by ETX<sup>®</sup> specifications), this kind of interface is realised using an LPC to ISA bridge (Fintek F85226AF).

All signals are 5V voltage tolerant.

Here following the signals related to the ISA Bus.

SD[0..15]: 16-bit System data bus, TTL bidirectional signals with  $8k2\Omega$  pull-up resistor to  $+5V_S$ .

SA[0..19]: System address bus, TTL bidirectional signals with  $8k2\Omega$  pull-up resistor to  $+5V_S$ . This bus allows addressing up to 1MB of ISA I/O space.

LA[17..23]: Latched address bus, TTL bidirectional signals with  $8k2\Omega$  pull-up resistor to  $+5V_S$ . Along with signals SA[0..16], this bus is used to address memory space up to 16MB.

SBHE#: System Byte High Enable, TTL bidirectional signal. It is asserted when a byte is transferred on data bus SD[8..15].

BALE: Bus Address Latch Enable, TTL bidirectional signal. It indicates that SA[0..19] bus, LA[17..23] bus and SBHE# signal are valid.

AEN: Address Enable, +5V tolerant output with 24mA source-sink capability. It indicates that a DMA cycle is currently performed.

MEMR#: Memory Read, TTL bidirectional signal with 8k2Ω pull-up resistor to +5V\_S. It is used to indicate that the current cycle is a memory read.

SMEMR#: System Memory Read, TTL output with 1kΩ pull-up resistor at +5V\_S. It is used to indicate that the current cycle is a system memory read under 1MB.

MEMW#: Memory Write, TTL bidirectional signal with 8k2Ω pull-up resistor to +5V\_S. It is used to indicate that the current cycle is a memory write.

SMEMW#: System Memory Write, TTL output with  $1k\Omega$  pull-up resistor at +5V\_S. It is used to indicate that the current cycle is a system memory write access under 1MB.

IOR#: I/O Read, TTL bidirectional signal with 8k2Ω pull-up resistor to +5V\_S. It is asserted to request an ISA I/O slave to drive data onto the data bus.

IOW#: I/O Write, TTL bidirectional signal with 8k2Ω pull-up resistor to +5V\_S. It is asserted to request an ISA I/O slave to accept the data currently available on the data bus.

IOCHK#: I/O Check, TTL input and Schmitt Trigger with 4k7Ω pull-up resistor to +5V\_S. This signal is driven by the ISA I/O devices to indicate that an error has occurred, therefore requiring a NMI.

IOCHRDY: I/O Check, TTL bidirectional signal with  $1k\Omega$  pull-up resistor to +5V\_S. When this signal is asserted, it means that an I/O device is requiring additional Wait states to complete its transactions.

M16#: 16-bit Memory Chip Select, TTL bidirectional signal with 1kΩ pull-up resistor to +5V\_S. This signal is activated (driven low) each time that the memory slave device supports 16-bit accesses.

IO16#:16-bit I/O Chip Select, TTL bidirectional signal with 1kΩ pull-up resistor to +5V\_S. This signal is activated (driven low) each time that the I/O device supports 16-bit I/O cycles.

REFSH#: Refresh Cycle indicator, output signal with 24mA source-sink capability, with  $1k\Omega$  pull-up resistor to +5V\_S. This signal is driven low each time that a refresh cycle is performed to prevent loss of memory contents.

NOWS#: No Wait States signal, TTL input and Schmitt Trigger with  $1k\Omega$  pull-up resistor to  $+5V_S$ . This signal is driven by the targeted I/O device each time it wants to signal that it is able to perform the transaction in the current cycle without needing additional wait states.

MASTER#: Master signal, TTL input and Schmitt Trigger with 8k2 $\Omega$  pull-up resistor to +5V\_S. When this input is activated (low), then a ISA bus master is currently driving the ISA bus. This signal is associated to a DREQ line by an ISA master when it wants take the control of the ISA Bus.

SYSCLK: ISA bus reference clock (circa 8MHz), output.

OSC: 14.318 MHz ISA Clock output.

RESETDRV: Reset, output signal with 24mA source-sink capability. It is used to reset external devices connected to ISA bus.

DREQ[0,1,2,3,5,6,7]: DMA request, TTL inputs (5V tolerant) with 8k2 $\Omega$  pull-down resistors. All of these signals can be driven by external devices when they need DMA access to the memory.

DACK[0,1,2,3,5,6,7]#: DMA request Acknowledge, 5V tolerant outputs with 24mA source-sink capability. These signals are asserted when it has been granted the DMA access on the corresponding DMA channel.

TC: Terminal Count signal, 5V tolerant output with 24mA source-sink capability. It signals the ending of a DMA transfer.

IRQ3, IRQ4, IRQ5, IRQ6, IRQ7, IRQ9, IRQ10, IRQ11, IRQ12, IRQ14, IRQ15: Interrupt Request lines (inactive high), TTL inputs with 8k2Ω pull-up resistors to +5V\_S.

ETX-A61 User Manual - Rev. First Edition: 1.0 - Last Edition: 1.2 - Author: S.B. - Reviewed by G.G. Copyright © 2017 SECO S.r.l.

### 3.2.5.4.1 ISA BUS LIMITATIONS

As already specified in the previous paragraph, the Intel<sup>®</sup> family of SoCs formerly coded as Bay trail do not support natively the ISA bus, which is required by ETX<sup>®</sup> specifications.

Therefore, this interface is realised using an LPC to ISA bridge (Fintek F85226AF), which causes the following limitations in using ISA Bus:

- DMA transfers are not supported;

- Memory Accesses are 8-bit at a time;

- It is not possible to access to any area located under 1MB because of Bay Trail's limits;

- Memory access in the 0xF0000000-0xF0FFFFF window are translated into ISA access in the range 0xF0000000 ÷ 0xF0FFFFFF, which is a 16MB-1 window

- Memory accesses in the area 0xF0000000-0xF00FFFF, i.e. accesses in the lower 1MB area translated in addressable area, are handled like if the access were above 1MB. This means that signals SMEMR# / SMEMW# will not change, only MEMR# and MEMW# will do.

#### 3.2.5.5 Analog VGA interface (Connector X3 - CN8)

The SOCs used on ETX-A61 module can manage directly one analog display interface, which can be used for the connection of older VGA/CRT displays.

Signals dedicated to VGA interface are the following:

- R: SOC's internal DAC's Red Signal video output.

- G: SOC's internal DAC's Green Signal video output.

- B: SOC's internal DAC's Blue Signal video output.

- HSY: SOC's internal DAC's Horizontal Synchronization output signal, electrical level +5V\_S.

VSY: SOC's internal DAC's Vertical Synchronization output signal, electrical level +5V\_S.

DDCK: internal DAC's DDC Clock line for VGA displays detection. Output signal, electrical level +5V\_S with  $2K2\Omega$  pull-up resistor.

DDDA: internal DAC's DDC Data line for VGA displays detection. Bidirectional signal, electrical level +5V\_S with  $2K2\Omega$  pull-up resistor.

Please be aware that for the connection to external VGA displays, on the carrier board it is necessary to provide for filters and ESD protection.

### 3.2.5.6 LVDS Flat Panel signals (Connector X3 - CN8)

The Intel<sup>®</sup> Bay Trail family of SOCs offer only two Digital Display Interfaces for the video, and doesn't offer the support for LVDS interface, which is conversely much used in many application fields, and is one of the two possible flat-panel interfaces required by the ETX<sup>®</sup> specifications.

For this reason, on ETX-A61 there is an eDP-to-LVDS bridge (NXP PTN3460), which allow the implementation of a Dual Channel LVDS, with a maximum supported resolution of 1920x1200 @ 60Hz (dual channel mode).

Here following the signals related to LVDS management:

LVDS\_A0+/LVDS\_A0-: LVDS Channel #A differential data pair #0.

LVDS\_A1+/LVDS\_A1-: LVDS Channel #A differential data pair #1.

LVDS\_A2+/LVDS\_A2-: LVDS Channel #A differential data pair #2.

LVDS\_A3+/LVDS\_A3-: LVDS Channel #A differential data pair #3.

LVDS\_CLK\_A+/LVDS\_CLK\_A-: LVDS Channel #A differential clock.

LVDS\_B0+/LVDS\_B0-: LVDS Channel #B differential data pair #0.

LVDS\_B1+/LVDS\_B1-: LVDS Channel #B differential data pair #1.

LVDS\_B2+/LVDS\_B2-: LVDS Channel #B differential data pair #2.

LVDS\_B3+/LVDS\_B3-: LVDS Channel #B differential data pair #3.

LVDS\_CLK\_B+/LVDS\_CLK\_B-: LVDS Channel #B differential Clock

BIASON: Analog Dimming, +5V signal, derived from the PWM signal LVDS\_BLT\_CTRL coming from COM Express module, for direct analogic control of backlights not supporting PWM.

DIGON: +3.3V\_S electrical level Output, Panel Power Enable signal. It can be used to turn On/Off the connected LVDS display.

BLON#: +3.3V\_S electrical level Output, Panel Backlight Enable signal. It can be used to turn On/Off the backlight's lamps of connected LVDS display.

LVDS\_BLT\_CTRL: this signal can be used to adjust the panel backlight brightness in displays supporting Pulse Width Modulated (PWM) regulations.

JILI\_DAT: DisplayID DDC Data line for LVDS flat Panel detection. Bidirectional signal, electrical level +3.3V\_S with a  $2k2\Omega$  pull-up resistor.

JILI\_CLK: DisplayID DDC Clock line for LVDS flat Panel detection. Bidirectional signal, electrical level +3.3V\_S with a  $2k^2\Omega$  pull-up resistor.

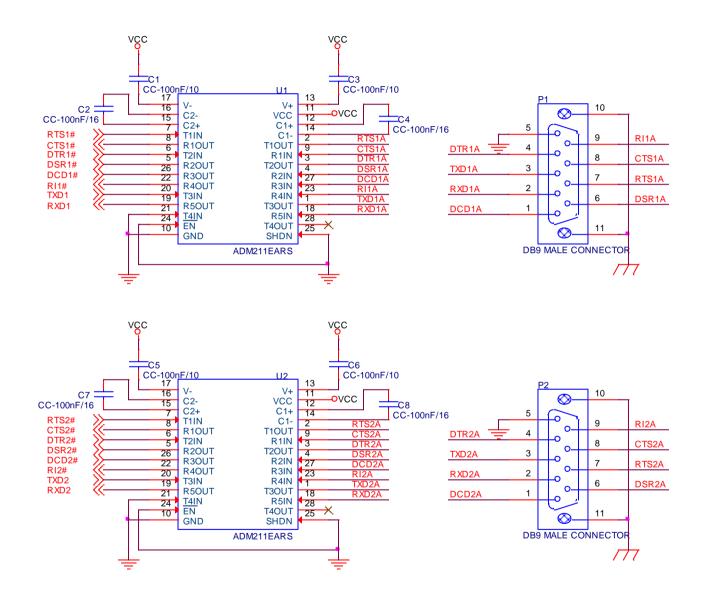

### 3.2.5.7 Serial port interface signals (Connector X3 - CN8)

According to ETX<sup>®</sup> Rel. 3.0 specifications, the ETX-A61 module offers two UART interfaces, which are managed by the LPC Super I/O Nuvoton W83627DHG.

Here following the signals related to UART interfaces:

DTR1#, DTR2#: Data Terminal Ready active low outputs, 3.3V\_S electrical level. This is a handshake signal used to notify to the DCE (Data Communication Equipment) that the DTE (Data Terminal Equipment) is ready to establish a data-communication link.

RI1#, RI2#: Ring Indicator active low inputs, 3.3V\_S electrical level. This is a handshake signal that the DCE uses to signal to the DTE that a telephone ring has been detected.

TXD1, TX2: Serial Data Transmitter outputs, 3.3V\_S electrical level.

RXD1, RXD2: Serial Data Receiver inputs, 3.3V\_S electrical level.

CTS1#, CTS2#: Clear To Send active low inputs, 3.3V\_S electrical level. This handshake signal is used to notify to the DTE that the DCE is ready to receive data-

RTS1#, RTS2#: Request to Send active low outputs, 3.3V\_S electrical level. These handshake signals are used to notify to the DCE that the DTE is ready to transmit data.

DCD1#, DCD2#: Data Carrier Detect active low inputs, 3.3V\_S electrical level. Handshake signal used to notify to the DTE that a carrier signal has been detected by the DCE.

DSR1#, DSR2#: Data Set Ready active low inputs, 3.3V\_S electrical level. Handshake signal used to notify to the DTE that the DCE is ready to establish a datacommunication link.