## Com express

## User Manual

## COMe-C42 BT7

COM-Express<sup>™</sup> Type 7 Module with the AMD EPYC<sup>™</sup> Embedded 3000 Series of SoCs.

## **REVISION HISTORY**

| F | Revision | Date         | Note                   | Rif |

|---|----------|--------------|------------------------|-----|

|   | 1.0      | 22 July 2021 | First Official Release | SB  |

|   |          |              |                        |     |

|   |          |              |                        |     |

All rights reserved. All information contained in this manual is proprietary and confidential material of SECO S.p.A.

Unauthorised use, duplication, modification or disclosure of the information to a third-party by any means without prior consent of SECO S.p.A. is prohibited.

Every effort has been made to ensure the accuracy of this manual. However, SECO S.p.A. accepts no responsibility for any inaccuracies, errors or omissions herein. SECO S.p.A. reserves the right to change precise specifications without prior notice to supply the best product possible.

For further information on this module or other SECO products, but also to get the required assistance for any and possible issues, please contact us using the dedicated web form available at http://www.seco.com (registration required).

Our team is ready to assist you.

## INDEX

| Chapter 1. INTRODUCTION              | 5  |

|--------------------------------------|----|

| 1.1 Warranty                         | 6  |

| 1.2 Information and assistance       | 7  |

| 1.3 RMA number request               | 7  |

| 1.4 Safety                           | 8  |

| 1.5 Electrostatic Discharges         | 8  |

| 1.6 RoHS compliance                  | 8  |

| 1.7 Safety Police                    |    |

| 1.8 Terminology and definitions      |    |

| 1.9 Reference specifications         | 12 |

| Chapter 2. OVERVIEW                  | 13 |

| 2.1 Introduction                     | 14 |

| 2.2 Technical Specifications         | 15 |

| 2.3 Electrical Specifications        | 16 |

| 2.3.1 Power Rails meanings           |    |

| 2.3.2 Power Consumption              |    |

| 2.4 Mechanical Specifications        |    |

| 2.5 Block Diagram                    |    |

| Chapter 3. CONNECTORS                | 20 |

| 3.1 Introduction                     | 21 |

| 3.2 Connectors' description          | 22 |

| 3.2.1 FAN Connector                  |    |

| 3.2.2 JTAG Connector                 |    |

| 3.2.3 SO-DIMM DDR4 Slots             |    |

| 3.2.4 BIOS Restore switch            |    |

| 3.2.5 COM Express® Module connectors |    |

| Chapter 4. BIOS SETUP                |    |

| 4.1 Aptio setup Utility              |    |

| 4.2 Main setup menu                  | 48 |

| 4.2.1      | System Date / System Time                                    | 48 |

|------------|--------------------------------------------------------------|----|

| 4.3 Adv    | ranced menu                                                  | 49 |

| 4.3.1      | AMD CBS Configuration submenu                                | 50 |

| 4.3.2      | iSCSI Configuration submenu                                  | 62 |

| 4.3.3      | Intel® I21x Gigabit Network Connection - MAC Address submenu | 62 |

| 4.3.4      | Battery Failure Manager submenu                              | 62 |

| 4.3.5      | Trusted computing submenu                                    | 63 |

| 4.3.6      | PSP Firmware Versions submenu                                | 63 |

| 4.3.7      | ACPI Settings submenu                                        |    |

| 4.3.8      | Board Parameters Setting submenu                             |    |

| 4.3.9      | S5 RTC Wake Settings submenu                                 |    |

| 4.3.10     | Serial Port Console Redirection submenu                      |    |

| 4.3.11     | CPU Configuration submenu                                    |    |

| 4.3.12     | PCI Subsystem Settings submenu                               |    |

| 4.3.13     | USB configuration submenu                                    |    |

| 4.3.14     | Network Stack configuration submenu                          | 68 |

| 4.3.15     | CSM configuration submenu                                    |    |

| 4.3.16     | NVMe configuration submenu                                   |    |

| 4.3.17     | SATA configuration submenu                                   |    |

| 4.3.18     | Main Thermal Configuration submenu                           |    |

| 4.3.19     | SMBIOS Information                                           |    |

| 4.3.20     | Embedded Controller submenu                                  |    |

|            | oset menu                                                    |    |

| 4.5 Sec    | curity menu                                                  | 76 |

| 4.5.1      | Secure Boot submenu                                          | 76 |

| 4.6 Boo    | ot menu                                                      | 77 |

| 4.7 Sav    | e & Exit menu                                                | 78 |

| 4.8 Eve    | nt Logs menu                                                 | 79 |

| 4.8.1      | Change Smbios Event Log Settings Submenu                     | 79 |

| Chapter 5. | Appendices                                                   |    |

| 5.1 The    | rmal Design                                                  | 81 |

|            |                                                              |    |

## Chapter 1. INTRODUCTION

- Warranty

- Information and assistance

- RMA number request

- Safety

- Electrostatic Discharges

- RoHS compliance

- Safety Police

- Terminology and definitions

- Reference specifications

## 1.1 Warranty

This product is subject to the Italian Law Decree 24/2002, acting European Directive 1999/44/CE on matters of sale and warranties to consumers.

The warranty on this product lasts 1 year.

Under the warranty period, the Supplier guarantees the buyer assistance and service for repairing, replacing or credit of the item, at the Supplier's own discretion.

Shipping costs that apply to non-conforming items or items that need replacement are to be paid by the customer.

Items cannot be returned unless previously authorised by the supplier.

The authorisation is released after completing the specific form available on the web-site <a href="http://www.seco.com/en/prerma">http://www.seco.com/en/prerma</a> (RMA Online). The RMA authorisation number must be put both on the packaging and on the documents shipped with the items, which must include all the accessories in their original packaging, with no signs of damage to, or tampering with, any returned item.

The error analysis form identifying the fault type must be completed by the customer and must accompany the returned item.

If any of the above mentioned requirements for RMA is not satisfied, the item will be shipped back and the customer will have to pay any and all shipping costs.

Following a technical analysis, the supplier will verify if all the requirements for which a warranty service applies are met. If the warranty cannot be applied, the Supplier will calculate the minimum cost of this initial analysis on the item and the repair costs. Costs for replaced components will be calculated separately.

Warning!

All changes or modifications to the equipment not explicitly approved by SECO S.p.A. could impair the equipments and could void the warranty

### 1.2 Information and assistance

What do I have to do if the product is faulty?

SECO S.p.A. offers the following services:

- SECO website: visit <a href="http://www.seco.com">http://www.seco.com</a> to receive the latest information on the product. In most cases it is possible to find useful information to solve the problem.

- SECO Sales Representative: the Sales Rep can help to determine the exact cause of the problem and search for the best solution.

- SECO Help-Desk: contact SECO Technical Assistance. A technician is at disposal to understand the exact origin of the problem and suggest the correct solution.

E-mail: technical.service@seco.com

Fax (+39) 0575 340434

- Repair centre: it is possible to send the faulty product to the SECO Repair Centre. In this case, follow this procedure:

- o Returned items must be accompanied by a RMA Number. Items sent without the RMA number will be not accepted.

- o Returned items must be shipped in an appropriate package. SECO is not responsible for damages caused by accidental drop, improper usage, or customer neglect.

Note: Please have the following information before asking for technical assistance:

- Name and serial number of the product;

- Description of Customer's peripheral connections;

- Description of Customer's software (operating system, version, application software, etc.);

- A complete description of the problem;

- The exact words of every kind of error message encountered.

## 1.3 RMA number request

To request a RMA number, please visit SECO's web-site. On the home page, please select "RMA Online" and follow the procedure described.

A RMA Number will be sent within 1 working day (only for on-line RMA requests).

## 1.4 Safety

The COMe-C42-BT7 module uses only extremely-low voltages.

While handling the board, please use extreme caution to avoid any kind of risk or damages to electronic components.

Always switch the power off, and unplug the power supply unit, before handling the board and/or connecting cables or other boards.

Avoid using metallic components - like paper clips, screws and similar - near the board when connected to a power supply, to avoid short circuits due to unwanted contacts with other board components.

If the board has become wet, never connect it to any external power supply unit or battery.

Check carefully that all cables are correctly connected and that they are not damaged.

## 1.5 Electrostatic Discharges

The COMe-C42-BT7 module, like any other electronic product, is an electrostatic sensitive device: high voltages caused by static electricity could damage some or all the devices and/or components on-board.

Whenever handling a COMe-C42-BT7 module, ground yourself through an anti-static wrist strap. Placement of the board on an anti-static surface is also highly recommended.

## 1.6 RoHS compliance

The COMe-C42-BT7 module is designed using RoHS compliant components and is manufactured on a lead-free production line. It is therefore fully RoHS compliant.

## 1.7 Safety Police

In order to meet the safety requirements of EN62368-1:2014 standard for Audio/Video, information and communication technology equipment, the COMe-C42 Module shall be:

- used inside a fire enclosure made of non-combustible material or V-1 material (the fire enclosure is not necessary if the maximum power supplied to the module never exceeds 100 W, even in worst-case fault);

- used inside an enclosure; the enclosure is not necessary if the temperature of the parts likely to be touched never exceeds 70 °C;

- installed inside an enclosure compliant with all applicable IEC 62368-1 requirements;

The manufacturer which includes a COMe-C42 module in his end-user product shall:

- verify the compliance with B.2 and B.3 clauses of the EN62368-1 standard when the module works in its own final operating conditions

- Prescribe temperature and humidity range for operating, transport and storage conditions;

- Prescribe to perform maintenance on the module only when it is off and has already cooled down;

- Prescribe that the connections from or to the Module have to be compliant to ES1 requirements;

- The module in its enclosure must be evaluated for temperature and airflow considerations.

## 1.8 Terminology and definitions

10GBASE-KR Backplane Ethernet, 10 Gbps datarate, designed to operate over a single lane with up to 1m (39") of copper PCB.

ACPI Advanced Configuration and Power Interface, an open industrial standard for the board's devices configuration and power management

AHCI Advanced Host Controller Interface, a standard which defines the operation modes of SATA interface

API Application Program Interface, a set of commands and functions that can be used by programmers for writing software for specific Operating

Systems

BIOS Basic Input / Output System, the Firmware Interface that initializes the board before the OS starts loading

BMC Baseboard Management Controller

DDR Double Data Rate, a typology of memory devices which transfer data both on the rising and on the falling edge of the clock

DDR4 DDR, 4th generation

DF Data Fabric

FCH Firmware Controller Hub, rhe integrated platform subsystem that contains the IO interfaces and bridges them to the system BIOS. Previously

included in the Southbridge

GbE Gigabit Ethernet

Gbps Gigabits per second

GT/s Gigatransfers per second

GND Ground

GPI/O General purpose Input/Output

12C Bus Inter-Integrated Circuit Bus, a simple serial bus consisting only of data and clock line, with multi-master capability

iSCSI Internet Small Computer Systems Interface, an Internet Protocol based storage networking standard for linking data storage facilities via networking.

LPC Bus Low Pin Count Bus, a low speed interface based on a very restricted number of signals, deemed to management of legacy peripherals

Mbps Megabits per second

NC-SI Network Controller Sideband Interface, electrical interface and protocol which enables the connection of a BMC to enable out-of-band remote

manageability.

N.A. Not Applicable N.C. Not Connected

NTB Non-transparent bridge. A device that links the memory space of two separate systems together. The processor implements a NTB that connects

two systems together using the PCI-e interface

OS Operating System

PCI-e Peripheral Component Interface Express

PWM Pulse Width Modulation

PWR Power

PXE Preboot Execution Environment, a way to perform the boot from the network ignoring local data storage devices and/or the installed OS

RAS Reliability, Availability and Serviceability, Reliability refers to the ability to detect errors. Availability is the ability to still operate in the face of failure.

Serviceability refers to capabilities that reduce the effort required to service a component.

SATA Serial Advance Technology Attachment, a differential half duplex serial interface for Hard Disks

SEV Secure Encrypted Virtualization

SEV-ES Secure Encrypted Virtualization Encrypted State

SM Bus System Management Bus, a subset of the I2C bus dedicated to communication with devices for system management, like smart batteries and

other power supply-related devices

SPI Serial Peripheral Interface, a 4-Wire synchronous full-duplex serial interface which is composed of a master and one or more slaves, individually

enabled through a Chip Select line

TBM To be measured

TLB Translation Lookaside Buffer, a memory cache that is used to reduce the time taken to access a user memory location

TTL Transistor-transistor Logic

UEFI Unified Extensible Firmware Interface, a specification defining the interface between the OS and the board's firmware. It is meant to replace the

original BIOS interface

USB Universal Serial Bus V REF Voltage reference Pin

xHCl eXtensible Host Controller Interface, Host controller for USB 3.0 ports, which can also manage USB 2.0 and USB1.1 ports

## 1.9 Reference specifications

Here below it is a list of applicable industry specifications and reference documents.

| Reference                           | Link                                                                                                                        |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| ACPI                                | http://www.uefi.org/acpi/specs                                                                                              |

| AHCI                                | http://www.intel.com/content/www/us/en/io/serial-ata/ahci.html                                                              |

| Com Express                         | https://www.picmg.org/openstandards/com-express/                                                                            |

| Com Express Carrier Design Guide    | http://picmg.org//wp-content/uploads/PICMG_COMDG_2.0-RELEASED-2013-12-061.pdf                                               |

| 10GBASE-KR                          | https://standards.ieee.org/standard/802_3ap-2007.html                                                                       |

| Gigabit Ethernet                    | https://www.techstreet.com/ieee/standards/ieee-802-3-2018?product_id=1999889                                                |

| I2C                                 | https://www.nxp.com/docs/en/user-guide/UM10204.pdf                                                                          |

| LPC Bus                             | https://www.intel.com/content/dam/www/program/design/us/en/documents/low-pin-count-interface-specification.pdf              |

| NC-SI                               | http://www.dmtf.org/sites/default/files/standards/documents/DSP0222 1.0.0.pdf                                               |

| PCI Express                         | http://www.pcisig.com/specifications/pciexpress                                                                             |

| SATA                                | https://www.sata-io.org                                                                                                     |

| SM Bus                              | http://www.smbus.org/specs                                                                                                  |

| UEFI                                | http://www.uefi.org                                                                                                         |

| USB 2.0                             | https://usb.org/document-library/usb-20-specification                                                                       |

| USB 3.x                             | https://usb.org/document-library/usb-32-specification-released-september-22-2017-and-ecns                                   |

| xHCl                                | http://www.intel.com/content/www/us/en/io/universal-serial-bus/extensible-host-controler-interface-usb-xhci.html?wapkw=xhci |

| AMD EPYC <sup>™</sup> Embedded 3000 | https://www.amd.com/en/products/embedded-epyc-3000-series                                                                   |

## Chapter 2. OVERVIEW

- Introduction

- Technical Specifications

- Electrical Specifications

- Mechanical Specifications

- Block Diagram

### 2.1 Introduction

The COMe-C42-BT7 is a COM Express® Type 7, basic Form Factor, based on the AMD EPYC™ Embedded 3000 3000 processors, specifically targeted for networking/server applications. The complete list of processors is available in the next chapter.

The main features of this new processor are I/O integration, flexibility, and security capabilities, scalable offering, harnessing the power of the new "Zen" CPU architecture.

Moreover, the performance is enhanced by the four DDR4 SO-DIMM slots supporting DDR4-2666 memory with ECC, up to 128GB.

This innovative solution provides scalable offerings with outstanding performance and connectivity, managing 4x 10GBASE-KR interfaces + 1x 1GbE port with NC-SI, four USB 3.1 ports and 24x PCI-e Gen3 lanes.

Please refer to following chapter for a complete list of all peripherals integrated and characteristics.

The product is COM Express® Rel.3.0 standard compliant, an open industry standard defined specifically for COMs (computer on modules). Its definition provides the ability to make a smooth transition from legacy parallel interfaces to the newest technologies based on serial buses available. Specifically, COMe-C42-BT7 is a COM Express® module, Basic Form factor, Type 7 (125mm x 95mm).

COM Express® module integrates all the core components and has to be mounted onto an application-specific carrier board; carrier board designers can utilize as little or as many of the I/O interfaces as deemed necessary. The carrier board can therefore provide all the interface connectors required to attach the system to the application specific peripherals. This versatility allows the designer to create a dense and optimised package, which results in a more reliable product while simplifying system integration. Most important, COM Express® modules are scalable, which means that once an application has been created there is the ability to diversify the product range through the use of different performance class or form factor size modules. Simply unplug one module and replace it with another, no redesign is necessary.

The robust thermal and mechanical concept, combined with extended power-management capabilities, is perfectly suited for all applications.

## 2.2 Technical Specifications

#### CPU

AMD EPYC<sup>™</sup> Embedded 3251, Eight Core Dual Thread @ 2.5GHz (3.1 Boost), 16MB L3 shared Cache, TDP 55W

AMD EPYC<sup>™</sup> Embedded 3201, Eight Core Single Thread @ 1.5GHz (3.1 Boost), 16MB L3 shared Cache. TDP 30W

AMD EPYC<sup>™</sup> Embedded 3151, Quad Core Dual Thread @ 2.7GHz (2.9 Boost), 16MB L3 shared Cache. TDP 45W

AMD EPYC<sup>™</sup> Embedded 3255, Eight Core Dual Thread @ 2.5GHz (3.1 Boost), 16MB L3 Shared Cache, TDP 25-55W, industrial grade

#### Memory

Up to 4x DDR4 SO-DIMM Slots supporting DDR4-2666 ECC and non-ECC Memory, up to 128GB

#### Mass Storage

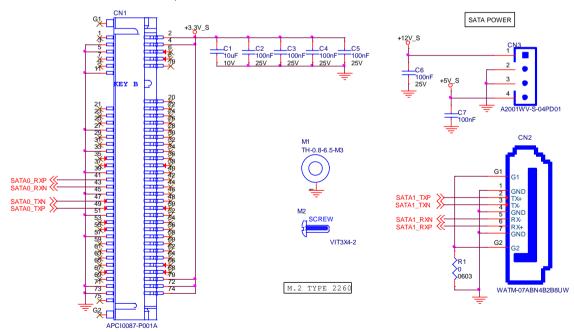

2 x external S-ATA Gen3 Channels

#### USB

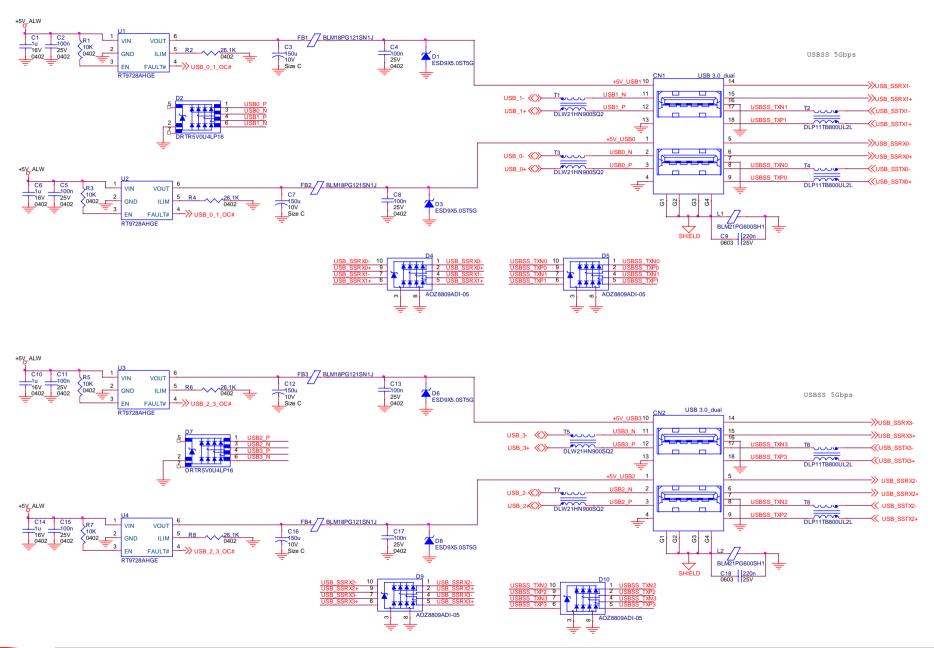

4 x USB 3.1 (SS+ USB 2.0 interfaces) Host ports

#### Networking

1x Gigabit Ethernet LAN port with NC-SI (Network Controller Sideband Interface) functionality, managed by an Intel® I210 Gigabit Ethernet Controller 4x 10Gigabit Ethernet interfaces (10GBASE-KR) directly managed by the EPYC™ Embedded 3000 SoC

#### PCI Express

24 x PCI-e Gen3 lanes

#### Serial Ports

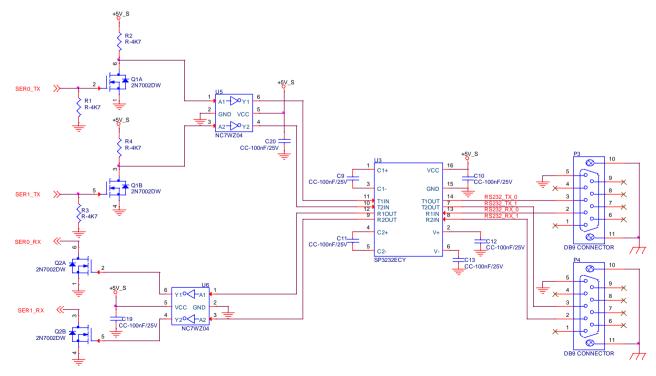

2 x legacy UARTs, 16C550 compatible

#### Other Interfaces

SPI, I2C, SM Bus, LPC bus Thermal Management, FAN management 4 x GPI, 4 x GPO LID# / SLEEP# / PWRBTN#, Watchdog Speaker Out Optional TPM 1.2 or 2.0 on-board Power supply voltage:  $+12V_{DC} \pm 10\%$  and  $+5V_{SB}$  (optional)

Operating System:

Microsoft® Windows 10 Enterprise (64-bit)

Microsoft® Windows Server 2016

Linux 64-bit

Operating temperature:

$0^{\circ}\text{C} \div +60^{\circ}\text{C}$  (Commercial version) \*\*

-40°C ÷ +85°C (Industrial version) \*\*

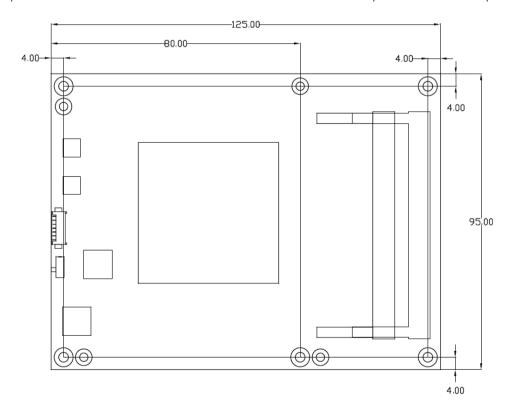

Dimensions: 125 x 95 mm

\*\* Temperatures indicated are the minimum and maximum temperature that the heatspreader / heatsink can reach in any of its parts. This means that it is customer's responsibility to use any passive cooling solution along with an application-dependent cooling system, capable to ensure that the heatspreader / heatsink temperature remains in the range above indicated. Please also check paragraph 5.1

## 2.3 Electrical Specifications

According to COM Express® specifications, the COMe-C42-BT7 board needs to be supplied only with an external +12V<sub>DC</sub> power supply.

5 Volts standby voltage needs to be supplied for working in ATX mode.

For Real Time Clock working and CMOS memory data retention, it is also needed a backup battery voltage. All these voltages are supplied directly through COM Express Connectors CN5-AB and CN5-CD.

All remaining voltages needed for board's working are generated internally from +12V<sub>DC</sub> power rail.

#### 2.3.1 Power Rails meanings

In all the tables contained in this manual, Power rails are named with the following meaning:

VCC\_5V\_SBY: 5V Standby voltage for the module

VCC\_12V: 12V Power In Voltage for the module.

\_RUN: Switched voltages, i.e. power rails that are active only when the board is in ACPI's S0 (Working) state. Examples: +3.3V\_RUN, +5V\_RUN.

\_ALW: Always-on voltages, i.e. power rails that are active both in ACPI's S0 (Working) and S5 (Soft Off) state. Examples: +5V\_ALW, +3.3V\_ALW. S3 (Standby) Status is not supported.

3.3V\_LAN: 3.3V always-on voltage, derived from 3.3V\_ALW, specifically used for 1GbE Ethernet section

#### 2.3.2 Power Consumption

COMe-C42-BT7 module, like all COM Express<sup>™</sup> modules, needs a carrier board for its normal working. All connections with the external world come through this carrier board, which provide also the required voltage to the board, deriving it from its power supply source.

Therefore, power consumptions of the board are measured using a CCOMe-C79 Carrier board on the dedicated +12V\_RUN power rail that supplies the board. For this reason, the values indicated in the table below are real power consumptions of the board and are independent from those of the peripherals connected to the Carrier Board.

Power consumption in Suspend and Soft-Off States have been measured on +5V\_ALW power rail. RTC power consumption has been measured on carrier board's backup battery when the system is not powered (VCC\_RTC power rail). For the measurements, it has been used a DC Power Analyzer Keysight N6700B.

The current consumptions, written in the table of next page, have been measured using the following setup:

**Board Configurations:**

- O.S. Windows 10

- 4x 32GB DDR4-2666 SO-DIMM, S-LINK J4BGDS2G8QHKC

- TPM Present, Ethernet Controller I210 or I211, 3-Wire FAN configuration, Commercial temperature range

### • USB mouse and keyboard connected

|                                                | CPU & board configuration                                      |       |                                                                |       |                                                                |       |                                                                |       |  |

|------------------------------------------------|----------------------------------------------------------------|-------|----------------------------------------------------------------|-------|----------------------------------------------------------------|-------|----------------------------------------------------------------|-------|--|

| Status                                         | AMD EPYC™<br>Embedded 3251<br>2.5GHz<br>I210 Eth<br>Controller |       | AMD EPYC™<br>Embedded 3201<br>1.5GHz<br>I210 Eth<br>Controller |       | AMD EPYC™<br>Embedded 3151<br>2.7GHz<br>I211 Eth<br>Controller |       | AMD EPYC™<br>Embedded 3101<br>2.1GHz<br>I211 Eth<br>Controller |       |  |

|                                                | Average                                                        | Peak  | Average                                                        | Peak  | Average                                                        | Peak  | Average                                                        | Peak  |  |

| Idle (Win 10), high performance configuration  | 1.19A                                                          | 1.46A | 1.20A                                                          | 1.88A | 1.13A                                                          | 1.84A | 1.10A                                                          | 1.69A |  |

| Idle (Win 10), power saving configuration      | 1.00A                                                          | 1.44A | 1.00A                                                          | 1.31A | 1.07A                                                          | 1.16A | 0.98A                                                          | 1.44A |  |

| Boot (Win 10), high performance configuration  | 3.10A                                                          | 5.27A | 2.14A                                                          | 3.14A | 1.97A                                                          | 2.92A | 2.14A                                                          | 2.95A |  |

| Internal Stress Test Tool, maximum performance | 4.70A                                                          | 4.76A | 2.42A                                                          | 2.49A | 2.84A                                                          | 2.85A | 2.84A                                                          | 3.00A |  |

| Soft Off (typical)                             | 139                                                            | mA    | 131                                                            | mA    | 128                                                            | mA    | 110                                                            | mA    |  |

## 2.4 Mechanical Specifications

The COMe-C42-BT7 is a COM Express board, Basic form Factor type; therefore its dimensions are 125 mm x 95 mm (4.92" x 3.74").

Printed circuit of the board is made of twelve layers, some of them are ground planes, for disturbance rejection.

According to COM Express specifications, the carrier board plug can be of two different heights, 5mm and 8mm.

Please be aware that the COMe-C42-BT7 module can be equipped with up to four SO-DIMM slots, where the secondary slot for each channel is located on bottom side of the module. In this case, SO-DIMM secondary slot for Channel #A is 4mm high, while secondary slot for Channel #B is 8mm high.

This means that, in order to deploy the maximum quantity of memory that can be managed by COMe-C42-BT7 module, it is necessary to consider a 8mm carrier board's plug height.

It is also necessary to avoid placing components on the carrier board in the zone under the COM Express® module, especially under the two SO-DIMM slots

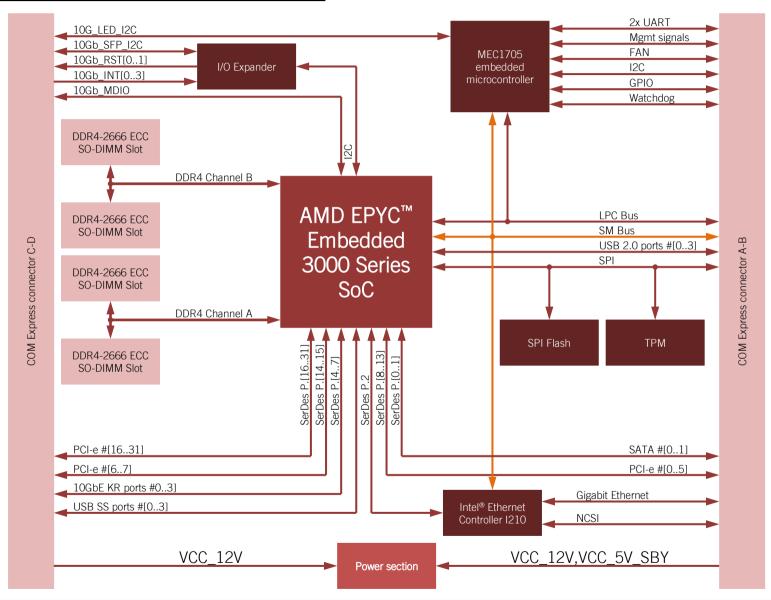

## 2.5 Block Diagram

# Chapter 3. CONNECTORS

- Introduction

- Connectors' description

## 3.1 Introduction

According to COM Express® specifications, all interfaces to the board are available through two 220 pin connectors, for a total of 440 pin. Simplifying the terminology in this documentation, the primary connector is called A-B and the secondary C-D, since each one consists of two rows.

In addition, a Fan connector has been placed on one side of the board, in order to allow an easier connection of active heatsinks to the module.

TOP SIDE

**BOTTOM SIDE**

SO-DIMM Slots

BIOS Restore switch

JTAG Connector

connector A-B

Connector

connector C-D

## 3.2 Connectors' description

#### 3.2.1 FAN Connector

| 3-W | 3-Wires FAN Connector - CN6 |  |  |  |  |  |  |  |  |

|-----|-----------------------------|--|--|--|--|--|--|--|--|

| Pin | Signal                      |  |  |  |  |  |  |  |  |

| 1   | GND                         |  |  |  |  |  |  |  |  |

| 2   | FAN_POWER                   |  |  |  |  |  |  |  |  |

| 3   | FAN_TACHO_IN                |  |  |  |  |  |  |  |  |

| 4-Wires FAN Connector –<br>CN7 |              |  |  |  |  |  |  |

|--------------------------------|--------------|--|--|--|--|--|--|

| Pin                            | Signal       |  |  |  |  |  |  |

| 1                              | GND          |  |  |  |  |  |  |

| 2                              | FAN_POWER    |  |  |  |  |  |  |

| 3                              | FAN_TACHO_IN |  |  |  |  |  |  |

| 4                              | FAN_PWM      |  |  |  |  |  |  |

Depending on the usage model of COMe-C42-BT7 module, for critical applications/environments on the module itself it is available a 3-pin dedicated connector for an external +12VDC FAN.

FAN Connector is a 3-pin single line SMT connector, type MOLEX 53261-0371 or equivalent, with pinout shown in the table on the left.

Mating connector: MOLEX 51021-0300 receptacle with MOLEX 50079-8000 female crimp terminals.

Please be aware that the use of an external fan depends strongly on customer's application/installation.

Please refer to chapter 5.1 for considerations about thermal dissipation.

As a factory alternative, onboard it is available a 4-pin connector, type MOLEX 53261-0371 or equivalent, with pinout shown in the table on the left.

Mating connector: MOLEX 51021-0300 receptacle with MOLEX 50079-8000 female crimp terminals.

Here following the description of the signals available on these connectors (FAN\_PWM available only on CN7 connector)

FAN\_POWER: +12V\_RUN derived power rail for FAN, managed by the embedded microcontroller via PWM signal.

FAN\_TACHO\_IN: tachometric input from the fan to the embedded microcontroller,  $+3.3V_RUN$  electrical level signal with  $10k\Omega$  pull-up resistor and Schottky diode.

FAN PWM: +3.3V RUN fan PWM input managed by the embedded microcontroller.

#### 3.2.2 JTAG Connector

| JTAG connector- CN8 |           |  |  |  |  |  |

|---------------------|-----------|--|--|--|--|--|

| Pin                 | Signal    |  |  |  |  |  |

| 1                   | +3.3V_ALW |  |  |  |  |  |

| 2                   | LM4_TMS   |  |  |  |  |  |

| 3                   | LM4_TCK   |  |  |  |  |  |

| 4                   | LM4_TDI   |  |  |  |  |  |

| 5                   | LM4_TD0   |  |  |  |  |  |

| 6                   | LM4_NRST  |  |  |  |  |  |

| 7                   | GND       |  |  |  |  |  |

The Embedded controller MEC1705 mounted on COMe-C42-BT7 module provides a JTAG interface, for test and debug purposes. This interface is available through an on-module connector, CN8, type MOLEX p/n 53261-0719. Mating connector MOLEX p/n 51021-0700 receptacle with 50079 female crimp terminals.

All these JTAG signals are at electrical level +3.3V ALW with 10k pull-up resistor and are directly connected to SOC pins with same name. Please refer to EPYC<sup>™</sup> Embedded 3000 family of processors documentation for a description of the signals and their usage.

LM4 TMS: JTAG Test Mode Select Signal, +3.3V ALW electrical level with 10k Ohm pull-up resistor.

LM4 TCK: JTAG Test Clock Signal, +3.3V ALW electrical level with 10k Ohm pull-up resistor.

LM4 TDI: JTAG Test Data Input Signal, +3.3V ALW electrical level with 1k Ohm pull-up resistor.

LM4 TDO: JTAG Test Data Output Signal, +3.3V ALW electrical level with 1k Ohm pull-up resistor.

LM4 NRST: JTAG Test Reset Output Signal, +3.3V ALW electrical level with 10k Ohm pull-up resistor.

#### SO-DIMM DDR4 Slots 3.2.3

CPUs used on the COMe-C42-BT7 board provide support to DDR4-2666 SO-DIMM memory modules. Both ECC and non-ECC modules are supported.

For use of this memories, on board there can be up to four SO-DIMM DDR4 slots.

The sockets placed on top side are CN1, type LOTES p/n ADDR0206-P003A or equivalent, and CN3, type LOTES p/n ADDR0070-P011A or equivalent. These sockets are always available.

The sockets placed on bottom side, instead, are optional. They are CN2, type LOTES p/n ADDR0205-P003A or equivalent, and CN4, type LOTES p/n ADDR0069-P011A or equivalent. CN2 is the secondary slot for memory Channel #A, CN4 is the secondary slot for memory Channel #B.

All of these sockets are right angle, low profile, standard type sockets, used for high speed system memory applications.

The four sockets together allow the insertion of up to 4 SO-DIMM modules, for support to four channel memories, reaching up to 128GB.

#### 3.2.4 **BIOS** Restore switch

In some cases, a wrong configuration of BIOS parameters could lead the module in an unusable state (e.g., all USB HID devices disabled).

For these cases, on the module it has been placed a 3-way switch SW1 which can be used to restore the BIOS to factory default configuration. To do so, it is necessary to place the contact of the switch in 1-2 position, then turn on the module, wait until the board has started regularly then turn off the module. The contact MUST be now placed back to 2-3 position.

During normal use, the contact MUST be always placed in 2-3 position.

T. . . . . . . . . . . . . . . . . .

#### 3.2.5 COM Express® Module connectors

For the connection of COM Express® CPU modules, on board there is one double connector, type TYCO 3-1827231-6 (440 pin, ultra thin, 0.5mm pitch, h=4mm), as requested by COM Express® specifications.

The pinout of the module is compliant to COM Express® Type 6 specifications. Not all the signals contemplated in COM Express® standard are implemented on the double connector, due to the functionalities really implemented on COMe-C42-BT7 board. Therefore, please refer to the following table for a list of effective signals reported on the connector. For accurate signals description, please consult the following paragraphs.

|              |      |                | COM Express® | Connec  | ctor CN | I – Rows A & B |       |              |

|--------------|------|----------------|--------------|---------|---------|----------------|-------|--------------|

|              |      | ROW A          |              |         |         |                | ROW B |              |

| SIGNAL GROUP | Type | Pin name       |              | Pin nr. | Pin nr. | Pin name       | Туре  | SIGNAL GROUP |

|              | PWR  | GND            |              | A1      | B1      | GND            | PWR   |              |

| GBE          | I/O  | GBE0_MDI3-     |              | A2      | B2      | GBE0_ACT#      | 0     | GBE          |

| GBE          | I/O  | GBE0_MDI3+     |              | А3      | В3      | LPC_FRAME#     | 0     | LPC          |

| GBE          | 0    | GBE0_LINK100#  |              | A4      | B4      | LPC_AD0        | I/O   | LPC          |

| GBE          | 0    | GBE0_LINK1000# |              | A5      | B5      | LPC_AD1        | I/O   | LPC          |

| GBE          | I/O  | GBE0_MDI2-     |              | A6      | В6      | LPC_AD2        | I/O   | LPC          |

| GBE          | I/O  | GBE0_MDI2+     |              | Α7      | В7      | LPC_AD3        | I/O   | LPC          |

| GBE          | 0    | GBE0_LINK#     |              | A8      | B8      | LPC_DRQ0#      | 1     | LPC          |

| GBE          | I/O  | GBE0_MDI1-     |              | Α9      | В9      | N.C.           | N.A.  |              |

| GBE          | I/O  | GBE0_MDI1+     |              | A10     | B10     | LPC_CLK        | 0     | LPC          |

|              | PWR  | GND            |              | A11     | B11     | GND            | PWR   |              |

| GBE          | I/O  | GBE0_MDI0-     |              | A12     | B12     | PWRBTN#        | 1     | PWR_MGMT     |

| GBE          | I/O  | GBE0_MDI0+     |              | A13     | B13     | SMB_CK         | I/O   | SMBUS        |

|              | N.A. | N.C.           |              | A14     | B14     | SMB_DAT        | 0     | SMBUS        |

| PWR_MGMT     | 0    | SUS_S3#        |              | A15     | B15     | SMB_ALERT#     | 1     | SMBUS        |

| SATA         | 0    | SATAO_TX+      |              | A16     | B16     | SATA1_TX+      | 0     | SATA         |

| SATA         | 0    | SATAO_TX-      |              | A17     | B17     | SATA1_TX-      | 0     | SATA         |

| PWR_MGMT     | 0    | SUS_S4#        |              | A18     | B18     | SUS_STAT#      | 0     | PWR_MGMT     |

| SATA         | I    | SATAO_RX+      |              | A19     | B19     | SATA1_RX+      | I     | SATA         |

| SATA         | I    | SATAO_RX-      |              | A20     | B20     | SATA1_RX-      | I     | SATA         |

|          | PWR  | GND         | A21 | B21 | GND         | PWR  |          |

|----------|------|-------------|-----|-----|-------------|------|----------|

|          | N.A. | N.C.        | A22 | B22 | N.C.        | N.A. |          |

|          | N.A. | N.C.        | A23 | B23 | N.C.        | N.A. |          |

| PWR_MGMT | 0    | SUS_S5#     | A24 | B24 | PWR_OK      | 1    | PWR_MGMT |

|          | N.A. | N.C.        | A25 | B25 | N.C.        | N.A. |          |

|          | N.A. | N.C.        | A26 | B26 | N.C.        | N.A. |          |

|          | N.A. | N.C.        | A27 | B27 | WDT         | 0    | MISC     |

|          | N.A. | N.C.        | A28 | B28 | N.C.        | N.A. |          |

|          | N.A. | N.C.        | A29 | B29 | N.C.        | N.A. |          |

|          | N.A. | N.C.        | A30 | B30 | N.C.        | N.A. |          |

|          | PWR  | GND         | A31 | B31 | GND         | PWR  |          |

|          | N.A. | N.C.        | A32 | B32 | N.C.        | N.A. |          |

|          | N.A. | N.C.        | A33 | B33 | I2C_CK      | 0    | I2C      |

| LPC      | 1    | BIOS_DISO#  | A34 | B34 | I2C_DAT     | I/O  | I2C      |

| MISC     | 0    | THRMTRIP#   | A35 | B35 | THRM#       | 1    | MISC     |

|          | N.A. | N.C.        | A36 | B36 | N.C.        | N.A. |          |

|          | N.A. | N.C.        | A37 | B37 | N.C.        | N.A. |          |

|          | PWR  | GND         | A38 | B38 | GND         | PWR  |          |

|          | N.A. | N.C.        | A39 | B39 | N.C.        | N.A. |          |

|          | N.A. | N.C.        | A40 | B40 | N.C.        | N.A. |          |

|          | PWR  | GND         | A41 | B41 | GND         | PWR  |          |

| USB      | I/O  | USB2-       | A42 | B42 | USB3-       | I/O  | USB      |

| USB      | I/O  | USB2+       | A43 | B43 | USB3+       | I/O  | USB      |

| USB      |      | USB_2_3_OC# | A44 | B44 | USB_0_1_OC# | I    | USB      |

| USB      | I/O  | USB_0-      | A45 | B45 | USB1-       | I/O  | USB      |

| USB      | I/O  | USB_0+      | A46 | B46 | USB1+       | 1/0  | USB      |

|          | PWR  | VCC_RTC     | A47 | B47 | N.C.        | N.A. |          |

|          | N.A. | N.C.        | A48 | B48 | N.C.        | N.A. |          |

| GBE      | I/O  | GBE0_SDP    | A49 | B49 | SYS_RESET#  | 1    | PWR_MGMT |

| LPC      | I/O  | LPC_SERIRQ  | A50 | B50 | CB_RESET#   | 0    | PWR_MGMT |

|          |      |             |     |     |             |      |          |

|      | PWR  | GND       | A51 | B51 | GND       | PWR  |          |

|------|------|-----------|-----|-----|-----------|------|----------|

| PCIE | Ο    | PCIE_TX5+ | A52 | B52 | PCIE_RX5+ | I    | PCIE     |

| PCIE | Ο    | PCIE_TX5- | A53 | B53 | PCIE_RX5- | I    | PCIE     |

| GPIO | I    | GPI0      | A54 | B54 | GPO1      | Ο    | GPIO     |

| PCIE | Ο    | PCIE_TX4+ | A55 | B55 | PCIE_RX4+ | I    | PCIE     |

| PCIE | 0    | PCIE_TX4- | A56 | B56 | PCIE_RX4- | I    | PCIE     |

|      | PWR  | GND       | A57 | B57 | GPO2      | Ο    | GPIO     |

| PCIE | 0    | PCIE_TX3+ | A58 | B58 | PCIE_RX3+ | I    | PCIE     |

| PCIE | Ο    | PCIE_TX3- | A59 | B59 | PCIE_RX3- | I    | PCIE     |

|      | PWR  | GND       | A60 | B60 | GND       | PWR  |          |

| PCIE | Ο    | PCIE_TX2+ | A61 | B61 | PCIE_RX2+ | I    | PCIE     |

| PCIE | 0    | PCIE_TX2- | A62 | B62 | PCIE_RX2- | I    | PCIE     |

| GPIO | 1    | GPI1      | A63 | B63 | GPO3      | Ο    | GPIO     |

| PCIE | 0    | PCIE_TX1+ | A64 | B64 | PCIE_RX1+ | I    | PCIE     |

| PCIE | Ο    | PCIE_TX1- | A65 | B65 | PCIE_RX1- | I    | PCIE     |

|      | PWR  | GND       | A66 | B66 | WAKEO#    | I    | PWR_MGMT |

| GPIO | 1    | GPI2      | A67 | B67 | WAKE1#    | I    | PWR_MGMT |

| PCIE | Ο    | PCIE_TX0+ | A68 | B68 | PCIE_RX0+ | I    | PCIE     |

| PCIE | Ο    | PCIE_TX0- | A69 | B69 | PCIE_RX0- | I    | PCIE     |

|      | PWR  | GND       | A70 | B70 | GND       | PWR  |          |

|      | N.A. | N.C.      | A71 | B71 | N.C.      | N.A. |          |

|      | N.A. | N.C.      | A72 | B72 | N.C.      | N.A. |          |

|      | PWR  | GND       | A73 | B73 | GND       | PWR  |          |

|      | N.A. | N.C.      | A74 | B74 | N.C.      | N.A. |          |

|      | N.A. | N.C.      | A75 | B75 | N.C.      | N.A. |          |

|      | PWR  | GND       | A76 | B76 | GND       | PWR  |          |

|      | N.A. | N.C.      | A77 | B77 | N.C.      | N.A. |          |

|      | N.A. | N.C.      | A78 | B78 | N.C.      | N.A. |          |

|      | PWR  | GND       | A79 | B79 | GND       | PWR  |          |

|      | PWR  | GND       | A80 | B80 | GND       | PWR  |          |

|      |      |           |     |     |           |      |          |

|          | N.A. | N.C.          | A81  | B81  | N.C.         | N.A. |          |

|----------|------|---------------|------|------|--------------|------|----------|

|          | N.A. | N.C.          | A82  | B82  | N.C.         | N.A. |          |

|          | PWR  | GND           | A83  | B83  | GND          | PWR  |          |

| NC-SI    | 1    | NCSI_TX_EN    | A84  | B84  | VCC_5V_SBY   | PWR  |          |

| GPIO     | 1    | GPI3          | A85  | B85  | VCC_5V_SBY   | PWR  |          |

|          | N.A. | N.C.          | A86  | B86  | VCC_5V_SBY   | PWR  |          |

|          | N.A. | N.C.          | A87  | B87  | VCC_5V_SBY   | PWR  |          |

| PCIE     | Ο    | PCIE_CLK_REF+ | A88  | B88  | BIOS_DIS1#   | 1    | LPC      |

| PCIE     | Ο    | PCIE_CLK_REF- | A89  | B89  | NCSI_RX_ER   | 0    | NC-SI    |

|          | PWR  | GND           | A90  | B90  | GND          | PWR  |          |

| SPI      | Ο    | SPI_POWER     | A91  | B91  | NCSI_CLK_IN  | I    | NC-SI    |

| SPI      | 1    | SPI_MISO      | A92  | B92  | NCSI_RXD1    | 0    | NC-SI    |

| GPIO     | Ο    | GPO0          | A93  | B93  | NCSI_RXD0    | 0    | NC-SI    |

| SPI      | Ο    | SPI_CLK       | A94  | B94  | NCSI_CRS_DV  | 0    | NC-SI    |

| SPI      | Ο    | SPI_MOSI      | A95  | B95  | NCSI_TXD1    | 1    | NC-SI    |

| MISC     | 1    | TPM_PP        | A96  | B96  | NCSI_TXD0    | 1    | NC-SI    |

| TYPE     | N.A. | TYPE10#: N.C. | A97  | B97  | SPI_CS#      | 0    | SPI      |

| UART     | Ο    | SERO_TX       | A98  | B98  | NCSI_ARB_IN  | 1    | NC-SI    |

| UART     | 1    | SERO_RX       | A99  | B99  | NCSI_ARB_OUT | 0    | NC-SI    |

|          | PWR  | GND           | A100 | B100 | GND          | PWR  |          |

| UART     | Ο    | SER1_TX       | A101 | B101 | FAN_PWMOUT   | 0    | MISC     |

| UART     | 1    | SER1_RX       | A102 | B102 | FAN_TACHIN   | 1    | MISC     |

| PWR_MGMT | 1    | LID#          | A103 | B103 | SLEEP#       | 1    | PWR_MGMT |

|          | PWR  | VCC_12V       | A104 | B104 | VCC_12V      | PWR  |          |

|          | PWR  | VCC_12V       | A105 | B105 | VCC_12V      | PWR  |          |

|          | PWR  | VCC_12V       | A106 | B106 | VCC_12V      | PWR  |          |

|          | PWR  | VCC_12V       | A107 | B107 | VCC_12V      | PWR  |          |

|          | PWR  | VCC_12V       | A108 | B108 | VCC_12V      | PWR  |          |

|          | PWR  | VCC_12V       | A109 | B109 | VCC_12V      | PWR  |          |

|          | PWR  | GND           | A110 | B110 | GND          | PWR  |          |

|          |      |               |      |      |              |      |          |

| ROW C   Fin nr.   Pin nr | Type<br>PWR<br>PWR<br>O | SIGNAL GROUP |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------|

| PWR         GND         C1         D1         GND           USB         GND         C2         D2         GND           USB         I         USB_SSRX0-         C3         D3         USB_SSTX0-           USB         I         USB_SSRX0+         C4         D4         USB_SSTX0+           PWR         GND         C5         D5         GND           USB         I         USB_SSRX1-         C6         D6         USB_SSTX1-           USB         I         USB_SSRX1+         C7         D7         USB_SSTX1+           PWR         GND         C8         D8         GND           USB         I         USB_SSRX2-         C9         D9         USB_SSTX2-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PWR<br>PWR<br>O         | SIGNAL GROUP |

| PWR         GND         C2         D2         GND           USB         I         USB_SSRX0-         C3         D3         USB_SSTX0-           USB         I         USB_SSRX0+         C4         D4         USB_SSTX0+           PWR         GND         C5         D5         GND           USB         I         USB_SSRX1-         C6         D6         USB_SSTX1-           USB         I         USB_SSRX1+         C7         D7         USB_SSTX1+           PWR         GND         C8         D8         GND           USB         I         USB_SSRX2-         C9         D9         USB_SSTX2-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PWR<br>O                |              |

| USB         I         USB_SSRX0-         C3         D3         USB_SSTX0-           USB         I         USB_SSRX0+         C4         D4         USB_SSTX0+           PWR         GND         C5         D5         GND           USB         I         USB_SSRX1-         C6         D6         USB_SSTX1-           USB         I         USB_SSRX1+         C7         D7         USB_SSTX1+           PWR         GND         C8         D8         GND           USB         I         USB_SSRX2-         C9         D9         USB_SSTX2-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Ο                       |              |

| USB         I         USB_SSRX0+         C4         D4         USB_SSTX0+           PWR         GND         C5         D5         GND           USB         I         USB_SSRX1-         C6         D6         USB_SSTX1-           USB         I         USB_SSRX1+         C7         D7         USB_SSTX1+           PWR         GND         C8         D8         GND           USB         I         USB_SSRX2-         C9         D9         USB_SSTX2-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |              |

| PWR         GND         C5         D5         GND           USB         I         USB_SSRX1-         C6         D6         USB_SSTX1-           USB         I         USB_SSRX1+         C7         D7         USB_SSTX1+           PWR         GND         C8         D8         GND           USB         I         USB_SSRX2-         C9         D9         USB_SSTX2-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                         | USB          |

| USB         I         USB_SSRX1-         C6         D6         USB_SSTX1-           USB         I         USB_SSRX1+         C7         D7         USB_SSTX1+           PWR         GND         C8         D8         GND           USB         I         USB_SSRX2-         C9         D9         USB_SSTX2-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                       | USB          |

| USB I USB_SSRX1+ C7 D7 USB_SSTX1+ PWR GND C8 D8 GND USB I USB_SSRX2- C9 D9 USB_SSTX2-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PWR                     |              |

| PWR GND C8 D8 GND USB I USB_SSRX2- C9 D9 USB_SSTX2-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                       | USB          |

| USB I USB_SSRX2- C9 D9 USB_SSTX2-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                       | USB          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PWR                     |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                       | USB          |

| USB I USB_SSRX2+ C10 D10 USB_SSTX2+                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                       | USB          |

| PWR GND C11 D11 GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PWR                     |              |